HTML5 compliant

|

Attention Different browsers interpret web page languages (HTML/ PHP/Javascript/CSS) differently at default. I tuned up this site best for Google Chrome, a most popular browser running on desktops/tablets/ notebooks/mobile phones. Other browsers (Firefox/Edge/IE/ Opera///) might exhibit weird appearance that I do not aim at. |

設計手法

日本と米国の半導体産業において種々の経験を積んできました。私の履歴書の一部ですが、その幅広い経験について簡潔にまとめた文章を添付しましょう。

要約

創造力と幅広い技術知識。日本と米国でそれぞれ16年以上大規模集積回路設計および管理実務を経験。電子卓上計算機用、ビデオゲーム用、CRTおよび液晶グラフィックス、

MPEGオーディオ・デコーダ、USBフラッシュメモリ・ブリッジなど先端集積回路製品の開発の第一線に従事。製品企画、アーキテクチャ/論理/回路/マスクレイアウト設計、テスト、

ブレッドボード/評価システム設計、ハードウエア/ソフトウエア設計、マーケティング/顧客訪問などを幅広く経験。複雑な問題を解決する卓越した解析力と直感力。

独創的なアイディアと行動を伴うリーダーシップ。常に先端技術を追究。

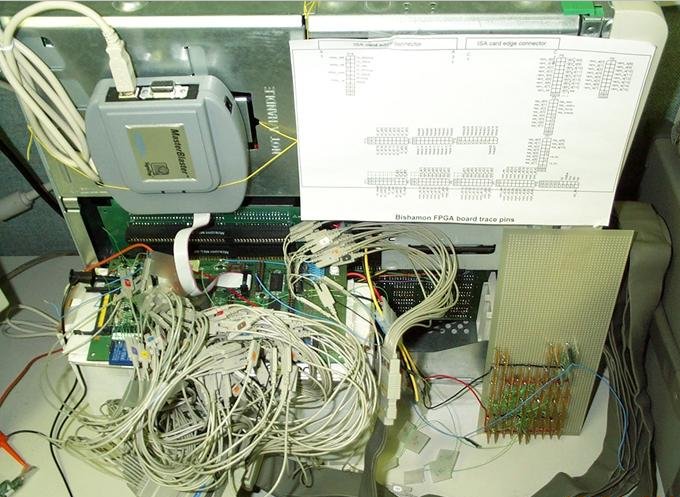

私達が大規模集積回路を開発する際、FPGAを活用することは実際の装置の元で機能確認をするために必須です。今日、FPGAは十分な速度とゲート規模を供給してくれています。

従って、UnixやPCのプラットフォームで動くベリログやVHDLのシミュレータやロジック・シンセサイザーを組み合わせつつ、FPGAによって機能検証の成されたVLSIを簡単に作ることができるようになりました。

昔は、ある種のLSIを開発するたびにTTLやPALを用いたブレッド・ボードを作らねばなりませんでした。1985年にNECで、µPD72120アドバンスト・グラフィックス・プロセッサーを開発した際に作った

ブレッド・ボードが最後のものとなりました。24インチ X 24インチの大きさの12枚のプリント基板を垂直の本立てに組み込み回転してデバグできるようになっている米国製のシステムを使いました。

可能な努力を一つ一つ積み重ねた結果、ようやく動作しましたが、その動作周波数はせいぜい2MHz足らずでした。その結果、後になって動作する試作品ができる以前にグラフィックス

BIOSを作ったり、顧客を訪問してデモンストレーション・システムを見せることができました。

今日、FPGAは驚異的に進歩しました。自動テスト・ベクター発生も近々供給されるようになり、テスト・ベクターをつくる努力をすることも必要なくなるでしょう。物性物理などの知識も無く

どのようにしてゲートがつくられるのか、どのようにテスト・ベクターをつくりVLSIを検査するかも知らないソフトウエア設計の人間が、あたかもソフトウエアをつくるが如くに、実際のシステムに

実装可能な商品を設計できるようになるのです。シリコン・ソフトウエアの時代がきました。

しかしながら、マスメディアの人間が描き、多くの人間が夢見ている想像上の楽天的世界とは異なり、現実の世界では、開発作業において幅広い領域を実際に経験したことがある人間

のみがすべてのことを効率的に効果的に処理していけるのです。そのような人は、ハードウエアとソフトウエア、デバイスとシステム、エンジニアリングとマーケティングのすべてに精通していなければ

なりません。最も重要な要素はそのような広範な経験に基づく直観力です。すぐさま、本物と偽物を区別することができる能力です。

2000年10月にサンタクララ・コンベンション・センターでBishamon(USB to CF/MMC/SD flash memory Bridge LSI)について講演しました。現在ではだれもが使っている

USBフラッシュメモリー・ステイックの原型となった集積回路で、その際、USBフラッシュメモリー・ステイックによるフロッピーディスクの置き換えについても予測しています。

高解像度スライド

実際に私がどのようにして物事を研究開発するのか、いくつかの簡単な事例をお示しします。この設計技法は大規模開発にも応用できることは言うまでもありません。

添付したPDFドキュメント・ファイルはブロック・ダイアグラム、タイミング・チャート、エミュレーション用Cソース・コード、ベリログHDLソース・コードやベリログ・シミュレーション結果としての

ウェーブ・フォームを含んでいます。

(1) NRZI (Non-Return-To-Zero) encoder & decoder

(2) CRC16 (Cyclic Redundancy Check: X16+X15+X2+X0) generator

(3) CRC5 (Cyclic Redundancy Check: X5+X2+X0) generator

(4) USB SIE (Universal Serial Bus Serial Interface Engine) receiver