#### NEC µPD7220/72120 Related Public Documents

- <u>ISSCC</u> (International Solid-State Circuit Conference)

- μPD7220A User's Manual

- Nikkei Electronics Magazine (µPD7220)

- Transistor Gijutsu (Technology) Magazine (<u>µPD7220</u>)

- Transistor Gijutsu (Technology) Magazine (µPD7220A)

- Nikkei Electronics Magazine (µPD72120)

- µPD72120 User's Manual

Go to <a href="https://www.oguchi-rd.com/LSI%20products.php">https://www.oguchi-rd.com/LSI%20products.php</a> to get more detailed NEC  $\mu$ PD7220/72120 related information such as;

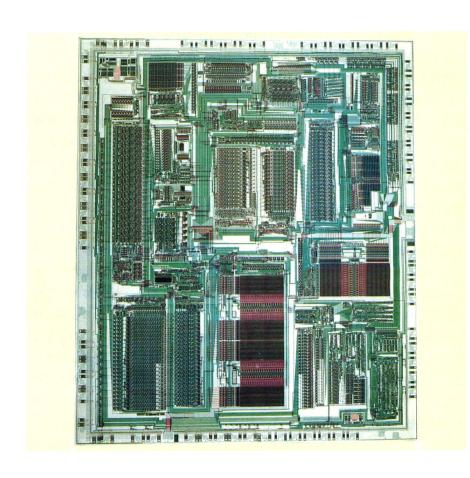

"Logic Schematics", "Design Notes", "Evaluation Board Schematics", "Evaluation Software", "Silicon Die Photos", "Newspaper", "Magazine", and so forth.

Go to <a href="https://www.oguchi-rd.com/patents.php">https://www.oguchi-rd.com/patents.php</a> to get patent information including NEC μPD7220/72120 related patents.

# μPD7220後継のグラフィックス・コントローラ LSI, コピーや塗りつぶし機能を強化

小口 哲司

大内 光郎

堀口 立二

千葉 俊和

日本電気 マイクロコンピュータ技術本部

鵜野 敬史

同 第一LSI事業部

日本電気は、グラフィックス・コントローラ LSI の新機種 AGDC (µPD72120) を開発した。1982 年に発売した GDC (µPD7220) の後継機で、ビットマップの処理機能を強化した点が特徴。拡大・縮小および回転を含んだ矩形領域のコピー機能、三角形、台形の塗りつぶし機能などを備えている。LSI 内部には描画用プロセサとは別に描画の前処理を実行するプリプロセサを搭載した。CPU、プリプロセサ、描画プロセサによる 3 段のパイプライン処理で、システムとしての性能を上げている。表示メモリの容量は最大 32 M バイトで、デュアル・ポート・メモリを使うことができる。最大 8 MHz で動作する。 (本誌)

#### μPD7220 後継のグラフィックス・コントローラ LSI、コピーや塗りつぶし機能を強化

|                                            | p.137 |

|--------------------------------------------|-------|

| デュアル・ポート・メモリなどで構成した最大 32 M バイトの表示メモリを制御できる | p.142 |

| パラメータ直接転送方式のコマンド・インタフェースを採用                | p.147 |

| 拡大・縮小,回転,塗りつぶしを高速処理する描画プロセサ                |       |

| 実際の実行速度を各種ベンチマーク・テストで評価                    | p.158 |

| OGI 準拠や高速化が可能                              | p.159 |

1981年2月に開催された ISSCC で,グラフィックス描画/表示用 LSI  $\mu$ PD7220(GDC)を発表した。それ以来,この製品はパーソナル・コンピュータをはじめとする OA機器,魚群探知機,写植機,衛星地上端末装置など幅広い分野に応用されてきた。GDC は,システム・バスから分離した最大 512 K バイトの表示メモリを直接制御できる。直線,円弧,グラフィックス文字などを高速に描画する機能を備えているり。GDC を用いると直線,円弧などの 1 次元的な描画は格段に速くなった。しかし,塗りつぶしやビットマップ・メモリに対する文字フォント展開など,いわゆる 2 次元的な(面に対する)描画機能は備えていない。このため,CPU でその機能を補完せねばならなかった。

このたび開発した µPD72120 (AGDC) では、CPUによる機能補完を最小限に抑えることをねらった。豊富な描画機能をグラフィックス・コントローラに付加するとともに、描画速度を高速化した。図形描画機能だけをとればGDC と比べて顕著な差異はない。ただし、楕円、弧、扇形、弦形などを一つのコマンドで描画できるように拡張した。

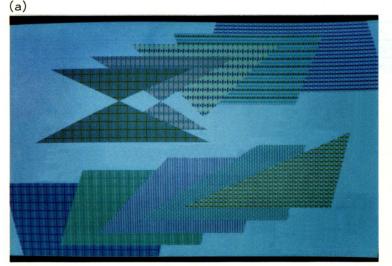

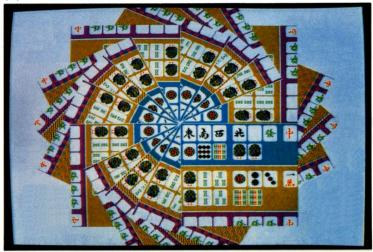

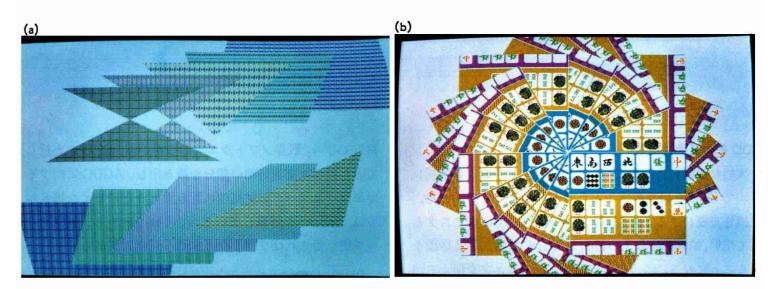

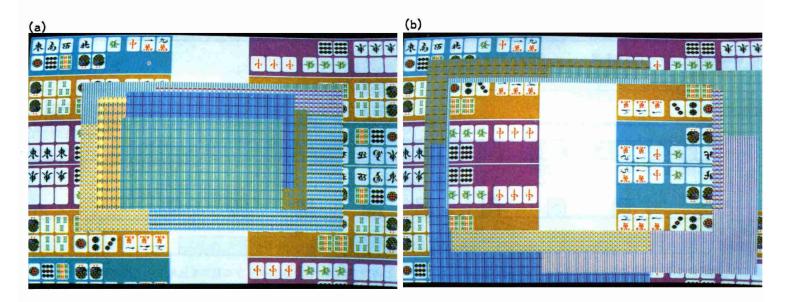

GDC に欠けていたビットマップ処理機能を積極的に搭載した。表示メモリ間のデータ転送(コピーあるいは bitblt機能),任意閉領域内の塗りつぶし(ペイント機能),円,楕円,三角形,台形内の無条件塗りつぶし(フィル機能)などである(図1(a))。このうちのコピー機能は,文字フォントの展開やウインドウの表示に重要な役割を果たす。コピー途中で図形を任意角度で傾斜,回転したり,制限はあるが任意倍率で拡大・縮小する機能も追加している(図1(b))。ビットマップ機能の強化に伴い,主記憶上に格納した1次元データを表示メモリ上に2次元的に展開するプット機能,その逆の動作をするゲット機能も付加した。

汎用のプロセサを使用してもこれらの機能を提供することはできる。しかし、十分な描画速度を期待することは現実的でない40。クロック周波数8 MHz のとき、AGDC の代表

的な描画速度を以下に示す。直線描画は、1 ドットまたは 1 ピクセルの描画を 500 ns で実行する。コピー機能を用いれば、1 秒間に 1 万 3640 字の  $24 \times 24$  ドット構成の文字フォントを展開できる。

#### 文字表示からグラフィックス表示へ急速に移行している

メモリの価格が下がるにつれ、ディスプレイの表示形態 は文字表示からグラフィックス表示へと急速に変化してき た。ワードプロセサなどでもグラフィックス・データを自 由に取り扱えることが最低条件とさえいわれ始めている。 ところが、グラフィックス表示は、大きなメモリ容量を必 要とし、制御も難しい。画面上の1文字を変更する場合, 文字表示では文字コード・メモリの内容を1バイトまたは 1ワード書き換えるだけですむ。一方,グラフィック ス表示では, 文字フォントを表示メモリ上に展開し直さな ければならない。CPUによる処理では書き換え速度が遅 すぎる。複雑な図形の塗りつぶしも、CPU には荷が重い。 このため,ゲートアレイなどを用いた専用回路を使って ビットマップに対し高速に描画する試みが成されてきた。 しかし、ゲートアレイ自身の集積度や速度の制約から、た とえば三角形塗りつぶしなどのマクロな描画を実行するこ とはできない。CPUが、細かい区切りで逐一、その描画に 関与する必要があった。細かい区切りを単位に描画速度を 評価すればゲートアレイは高速である。しかし,システム 全体として評価した場合には、期待したほどのパフォーマ

このような背景から、GDC の発表以後、描画機能などを 強化したグラフィックス・コントローラ LSI が多数登場し た。表 1 にコントローラの代表的な機能を取り上げて、主 な LSI を比較してみた。これらの製品は各社の設計思想の 違いから、それぞれ異なった特徴を備えている。Am95C60 (米 Advanced Micro Devices, Inc.) と AGDC はハードウ

ンスを得られない場合が多い。

エアによる高速描画機能の実現を重視している。HD63484 (日立製作所) はさらに表示制御機能を生かそうとした。 82786 (米 Intel Corp.) は主に表示制御機能を充実しようと し、TMS34010 (米 Texas Instruments Inc.) は汎用型プ ロセサを内蔵し自由に描画ソフトウエアを作成できるよう にしている。

グラフィックスに関してもう一つの重要な動きがある。 ライン・バッファを内蔵したデュアル・ポート・メモリの 出現である。最初の製品は、シリアル・メモリ型のライン ・バッファを内蔵した 64 K ダイナミック RAM であっ た2)。その後、ライン・バッファをランダム・アクセス型と し、リアルタイム・データ転送機能、ポインタ・コントロ ール機能、ライト・パー・ビット機能などを盛り込んだ256 K デュアル・ポート・メモリが発表された<sup>3)</sup>。

デュアル・ポート・メモリを表示メモリとして使用する と、描画可能なタイミングが格段に増加する。これは、連 続描画が可能なコントローラの実力を引き出すのに有効で ある。

#### システムとしての性能向上をねらう

AGDC はデュアル・ポート・メモリの制御機能を備えて いる。また、CPUと組み合わせたシステムとしての性能を 上げることを念頭に置いて設計した。内部はマルチプロセ サ構成のアーキテクチャを採用している。AGDC 内には描 画を実行する描画プロセサとは別に、プリプロセサという 描画前処理用のプロセサをもたせた。

プリプロセサは X-Y 座標から絶対アドレスへのアドレ ス変換などの描画前処理を実行する。コマンド・インタフ ェースとしては CPU がプリプロセサの内蔵レジスタへコ マンド・パラメータを直接書き込む方法を採用した。プリ プロセサは描画を実行する描画プロセサとは独立に動作す る。この結果, CGI や BASIC などの命令解釈や AGDC の 駆動など、CPU が実行する描画前処理と、プリプロセサに よる描画前処理, さらには描画プロセサによる描画実行と を、システム的にみて3段のパイプラインで処理すること ができる。

さらに、描画速度そのものを向上させるため、描画アル ゴリズムの検討段階に、そのアルゴリズムに適した特殊な 基本ハードウエアを設計した。描画プロセサは,これらの ハードウエアを密に制御し、描画種類が変化しても応用が 効くように設計している。ちなみに、1クロック125 ns (8 MHz 時)で実行する各ステップで、最大6種類の命令実行 および直接分岐を実行できる。各命令の実行にはパイプラ イン処理的な命令先取り機能をもたせている。したがって, この描面プロセサ自身も並列処理とパイプライン処理とを 併せ持つ形態になっている。

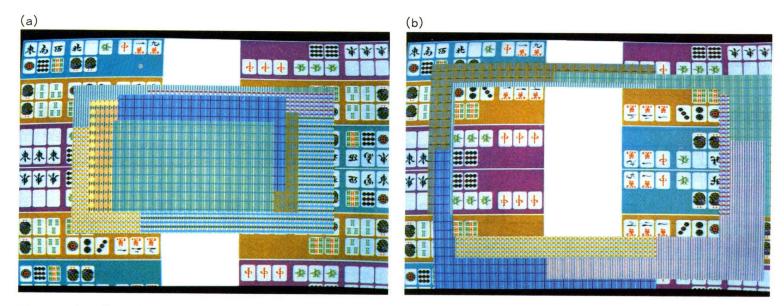

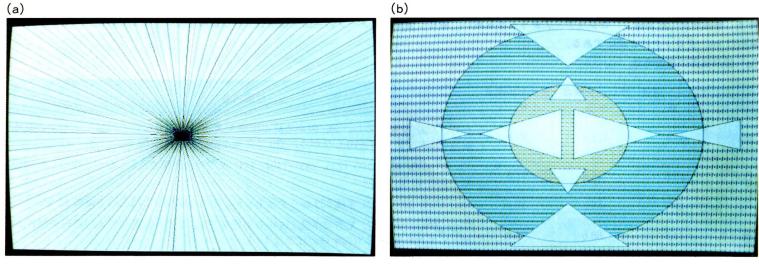

(b)

640×480ドットの表示画面を用いた。(a)は頂点の座標をパラメータとする一つのコマンドで台形を塗りつぶした。(b)は矩形 領域の回転コピー結果である。倍率一定のまま回転すると1辺の長さが変わるため,回転角度に従って縮小処理を実行している。

表1 主なグラフィックス・コントローラの機能比較 機能としては備えているが実用上不十分と思われるものを"△"とした。機能の一部しかないときは"○"とした。ソフトウエアによってその機能を実現できるものについては"──"とした。

|                     | HD63484<br>(日立製作所) | Am95C60<br>(Advanced Micro)<br>Devices, Inc. | TMS34010<br>(Texas<br>Instruments Inc.) | 82786<br>(Intel Corp.)                  | μ <b>PD72120</b><br>(日本電気)              |

|---------------------|--------------------|----------------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|

| ▷描画機能               |                    |                                              |                                         |                                         |                                         |

| 直線・四辺形              | 0                  | 0                                            | 0                                       | 0                                       | 0                                       |

| 円•円弧                | 0                  | 0                                            |                                         | 0                                       | 0                                       |

| 楕円•楕円弧              | 0                  | ×                                            |                                         | ×                                       | 0                                       |

| 扇形·弦形               | ×                  | ×                                            |                                         | ×                                       | 0                                       |

| 任意閉領域内塗りつぶし         | Δ                  | 0                                            |                                         | ×                                       | 0                                       |

| 四辺形内塗りつぶし           | 0                  | 0                                            |                                         | ×                                       | 0                                       |

| 円・楕円内塗りつぶし          | ×                  | 0                                            |                                         | ×                                       | 0                                       |

| 三角形内塗りつぶし           | ×                  | 0                                            |                                         | ×                                       | 0                                       |

| 台形内塗りつぶし            | ×                  | ×                                            |                                         | ×                                       | 0                                       |

| ▷表示メモリ内データ転送        |                    |                                              |                                         |                                         |                                         |

| 通常コピー               | 0                  | 0                                            | 0                                       | 0                                       | 0                                       |

| 90 度回転コピー           | 0                  | 0                                            |                                         | 0                                       | 0                                       |

| 傾斜コピ                | ×                  | ×                                            | -                                       | ×                                       | 0                                       |

| 拡大・縮小コピー            | ×                  | 0                                            |                                         | ×                                       | 0                                       |

| 任意角回転を含む拡大・縮小コピー    | ×                  | ×                                            |                                         | ×                                       | 0                                       |

| ▷ハードウエア・クリッピング      | 0                  | 0                                            | ×                                       | 0                                       | 0                                       |

| □プット・ゲット            | ×                  | 0                                            |                                         | ×                                       | 0                                       |

| ▷描画位置指定             | X-Y 座標             | X-Y 座標                                       | X-Y 座標                                  | <ul><li>X-Y 座標</li><li>絶対アドレス</li></ul> | <ul><li>X-Y 座標</li><li>絶対アドレス</li></ul> |

| ▷表示メモリ構成(最大容量)      | ピクセル型<br>(2 M バイト) | プレーン型<br>(8 M バイト)                           | ピクセル型<br>(128 M バイト)                    | ピクセル型<br>(4 M バイト)                      | プレーン型,<br>ピクセル型<br>(32 M バイト)           |

| ▷表示メモリの CPU へのマッピング | ×                  | ×                                            | ×                                       | 0                                       | 0                                       |

| ▷デュアル・ポート・メモリ制御     | ×                  | 0                                            | 0                                       | 0                                       | 0                                       |

| ▷描画と描画前処理の分離        | ×                  | ×                                            | ×                                       | ×                                       | 0                                       |

| ▷表示と描画のクロック分離       | ×                  | 0                                            | ×                                       | ×                                       | 0                                       |

| ▷表示機能               |                    |                                              |                                         |                                         |                                         |

| 画面分割                | 0                  | ×                                            | ×                                       | 0                                       | ×                                       |

| 拡大表示                | 0                  | ×                                            | ×                                       | 0                                       | ×                                       |

| ハードウエア・ウインドウ        | Δ                  | Δ                                            | ×                                       | 0                                       | ×                                       |

| カーソル出力              | 0                  | ×                                            | X                                       | 0                                       | 0                                       |

#### GDC との互換性はない

大幅な機能向上を意図したので、コマンドおよび機能レベルで GDC との互換性をもたせることはできなかった。 互換性を維持するためには、従来どおり GDC をマスタと して用い、描画機能向上の目的で AGDC を付加する構成を 採ることになる。こうすれば既存ソフトウエアを使えるが、 AGDC の機能を利用することはできない。しかし、AGDC を利用するルーチンを既存ソフトウエアに追加することは 難しくない。既存ソフトウエアのなかから、CPUが実行していた複雑な描画処理の部分を抜き出し、AGDCに対する簡単なパラメータ転送処理に置き換えるだけですむ場合が多い。AGDCを搭載しているかどうかを判定し、制御フローを切り替えればソフトウエアの一元化も図れる。

AGDC は、パーソナル・コンピュータ、ワードプロセサ、ワークステーション、レーザ・プリンタなど、グラフィックス機能を必要とするすべての分野への応用をねらっている。

### マルチプロセサ構成の内部アーキテクチャ

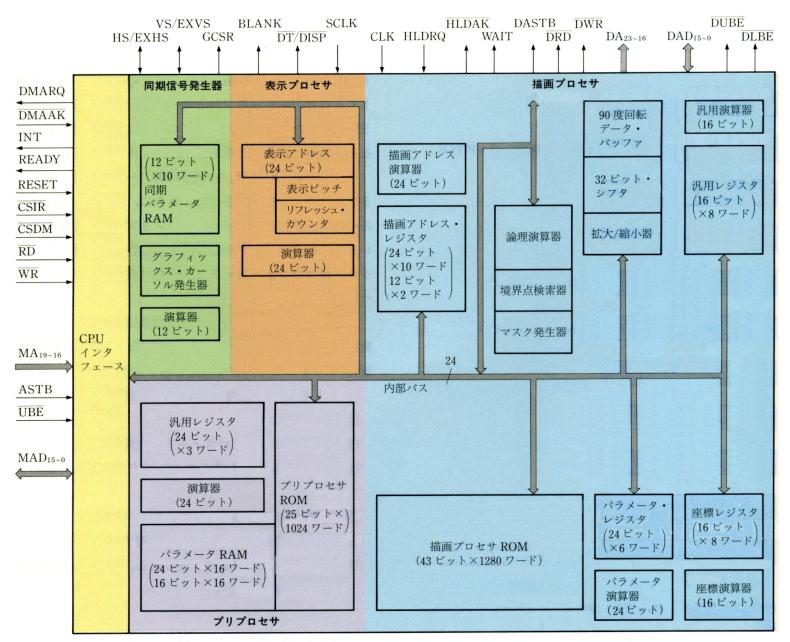

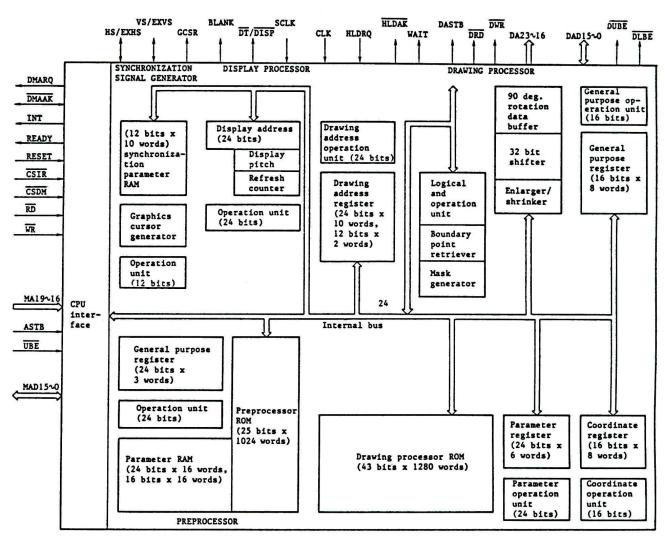

AGDC の内部は以下に示す 5 種類の内部機能ブロック に分かれている(図2)。

- ① プリプロセサ

- ② 描画プロセサ

- ③表示プロセサ

- ④ 同期信号発生器

- ⑤ CPU インタフェース

描画、表示、前処理用に3種のプロセサを搭載するマル

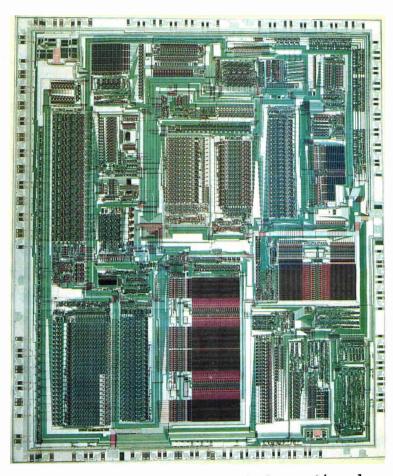

図2 内部構成 同期信号発生器、表示プロセサ、プリプロセサ、描画プロセサ、CPU インタフェースという 5 種類の機能ブロックで構成する。 各ブロック間は 24 ビットの内部バスで結ぶ。アーキテクチャの特徴は,プリプロセサと描画プロセサでパイプライン処理を行なうこと,描画プロ セサ内に高速の塗りつぶしや拡大・縮小を行なうハードウエアをもたせたことである。

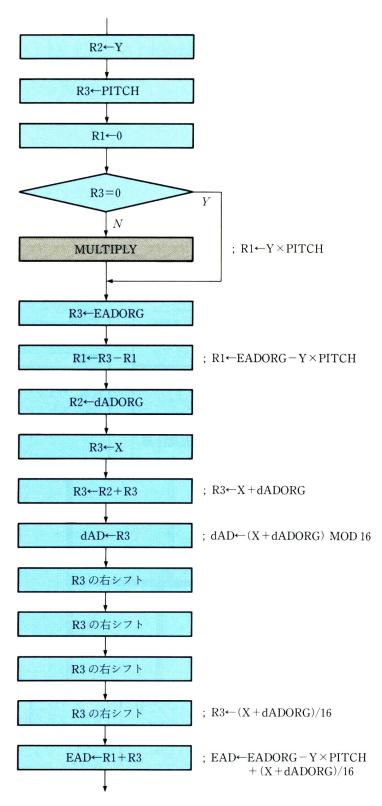

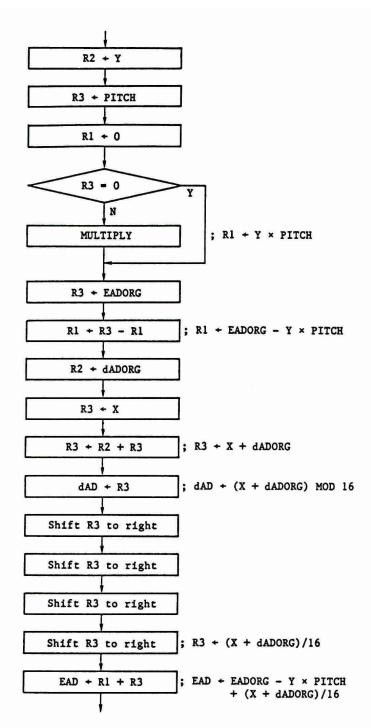

図3 X-Y座標から絶対アドレスを計算するプリプロセサの処理手 一つのステップを 1 クロック(8 MHz 時には 125 ns) で実行でき る。プリプロセサ内の加減算器で図中に示した MULTIPLY という乗算 を実行する。プリプロセサを搭載したことで、描画前処理は CPU で処 理する場合より 10 倍程度速くなった。

チプロセサ構成を採用した点がアーキテクチャの特徴であ る。この構成により、CPU、プリプロセサ、描画プロセサ というパイプライン処理を可能にした。また、描画プロセ サには描画速度を上げるための専用ハードウエアをもたせ ている。

#### プリプロセサで描画の前処理を実行

GDC は CPU からコマンドを受け取るための FIFO を内蔵していた。主に描画速度と前処理速度の違いを調整 するためである。しかし、この FIFO にはコマンド・パラ メータを一時的に記憶する受動的な役割しかない。一方, 集積度の向上で、X-Y 座標からメモリの絶対アドレスを算 出するなどの前処理をコントローラに分担させる方向が一 般的になった。ただし、描画プロセサにこの機能を追加す ると, 前処理と描画とを並列に実行できなくなる。

そこで、AGDCでは、描画前処理の一部を高速に実行す るプリプロセサを内蔵させた。さらに、受動的な FIFO へ のパラメータ書き込みではなく、プリプロセサの管理する レジスタへパラメータを直接書き込む方式を採用した。レ ジスタにコマンド・コードを書いた時点から、プリプロセ サは動作を開始する。

プリプロセサは、24ビットの加減算器、汎用レジスタ、 制御 ROM, パラメータ RAM などで構成している(図2参 照)。プリプロセサの主な機能を以下に示す。

- ① X-Y 座標から絶対アドレスへの変換

- ② コマンドの解釈

- ③ 図形描画に必要なパラメータの生成

- ④ Y 座標を基にした塗りつぶしパターン抽出位置の算

- ⑤ 三角形塗りつぶしのための座標のソーティング

- ⑥ ユーザの設定したパラメータに対するエラー·チェック

- ⑦ 描画プロセサとのデータ受け渡し、および、描画プロ セサの起動制御

#### X-Y 座標から物理アドレスを高速に計算

プリプロセサは X-Y 座標から表示メモリの絶対アドレ スを計算する。次の計算式を用いると座標(X-Y)から絶対

命令は43ビット長で、AからFまでの6種類のフィールドから成る。各フィールドの命令は他のフィールドと独 図 4 描画プロセサの命令形式 立して実行できる。演算器やシフタの数はフィールド数よりも多いので、一つのフィールドで複数の演算を制御できる。

ワード・アドレス EAD、ドット・アドレス dAD を算出で きる。

$$EAD = EADORG - Y \times PITCH$$

$$+\{(X+dADORG)/16\}$$

(1)

$$dAD = (X + dADORG) MOD 16$$

(2)

EADORG と dADORG は X-Y 座標の原点 (0,0) に相当 する絶対アドレス (それぞれワード・アドレスとドット・ アドレス)を示す。PITCH は表示メモリの水平方向のワー ド数である。

プリプロセサはこの計算式に従うアドレス計算を最小の ハードウエアで高速に実行する。そのために既存の汎用プ ロセサを流用するという安易な方法は採らなかった。処理 の高速化や無駄を省いた回路構成とするには, 最適化され たプロセサを新たに設計する必要があったからである。プ リプロセサの24ビット加減算器を用いると、たとえば、乗 数と被乗数が16ビットで積が24ビットの乗算を,1ビッ ト当たり1クロックで実行できる。この速度を実現するた めに、3本の演算レジスタ中の1本に右シフタ、他の1本に 左シフタを付加した。また加減算器に演算終了判定回路を 組み込んだ。このハードウエアは整数除算も高速に実行で きる。

アドレス計算の流れを図3に示す。図中のMUL-TIPLY (Y×PITCH) というのが加減算器による乗算を示 している。表示画面の水平解像度が1024画素のとき、その ワード数を表す PITCH は 64 (実質 7 ビット) である。し たがって、この乗算は7クロックで実行できる。X-Y座標 から物理アドレスへの変換は、この7クロックに、他のス テップ (図3参照) を加えた22クロックで実行することに なる。

#### 描画プロセサに

#### 拡大・縮小、境界点検索などを行なうハードウエアを搭載

プリプロセサは一つの演算器しか備えていない。一方, 描画プロセサは描画を高速化するために複数の演算器やシ フタ,マスク生成器などを備えている。これらの回路は一 つのサイクル内で同時に制御できるようにしてある。命令 は43ビット幅で,6種のフィールドから成る。その各フィ ールドに異なるハードウエアの制御を受け持たせた(図 4)。最大2種類の判定結果によるアドレスの4分岐も,一 つのサイクル内に実行できる。したがって,アドレス分岐 や演算命令などをすべて1クロック(125 ns)で実行でき る。たとえば、24ビットのレジスタ読み出し、演算、再書き 込み、演算結果の判定は1クロックで終了する。

この処理速度を達成するために、制御記憶を高速にアク セスする工夫を施した。非同期型の ROM を用いることで、 アドレスを与えればすぐに出力が得られるようにした。し かし、アドレス・サイクルに同期して命令を取り出すため に、すべての命令デコード出力ドライバに同期型一時記憶 素子を付加する回路構成を採った。これにより制御 ROM はすべて1サイクルでアクセスできる。

描画プロセサの24ビットの描画アドレス演算器,描画パ ラメータ演算器、16ビットの座標演算器、汎用演算器など にはそれぞれ密に接続したレジスタ群をもたせている。こ のほかにも表示データ論理演算器,90度回転データ・バッ ファ,32ビット・シフタ,データ拡大/縮小回路,描画マス ク発生器, 境界点検索器などのハードウエアを満載してい る (図2参照)。

傾斜コピーでは1本の直線発生器,三角形や台形フィル, 任意角回転コピーでは2本の直線発生器,円や楕円フィル

では1個の円・楕円発生器を使用して必要な座標を発生させている。こうした座標発生器を固定機能のハード・ワイヤド・ロジックで組み込んだわけではない。描画プロセサはソフトウエア変更だけで、共通なハードウエアをさまざまな用途に効率よく使えるようにしてある。たとえば、直線発生器はパラメータ・レジスタ3本とワーキング・レジスタ1本で構成している。

また、AGDCはピクセルまたはドット単位で描画する機能と、ワード単位で描画する機能を併せ持っている。異なる描画に対しても不都合なく動作するように描画マスク発生器を新たに開発した。このなかにクリッピング制御器も含めている。マスク発生、クリッピング制御は他の描画処理と並列に動作する。したがって、クリッピング動作を指示しても描画速度は遅くならない。

#### 複雑な描画は分割し、プリプロセサと描画プロセサで パイプライン処理

座標レジスタや描画用アドレス・レジスタなどは描画プロセサとプリプロセサの両方にもたせた。このため、プリプロセサが処理を終了している状態であればプリプロセサのレジスタ内容を更新しても描画動作には影響しない。プリプロセサと描画プロセサは各々の処理を独立に実行できることになる。その結果、描画プロセサが描画実行中に、プリプロセサは次の描画のための前処理を実行できる。

プリプロセサには描画プロセサの状態検出機能に加え, 起動指示機能ももたせた。したがって,一つの描画コマン ドであっても,描画プロセサの動作を何回かに分けて指示 することができる。たとえば,円弧扇形描画の場合,実際 は次のように処理を進めている。

- ① 円弧の描画パラメータ算出 (プリプロセサ)。

- ②円弧の描画(描画プロセサ)。

- ③ 描画の開始点および終了点を描画プロセサから読み 出した後,終了点と中心間の直線描画パラメータ算出 (プリプロセサ)。

- ④ 終了点と中心間の直線描画(描画プロセサ)。 中心-開始点間の直線描画パラメータ算出(プリプロセサ)。

⑤ 中心-開始点間の直線描画(描画プロセサ)。

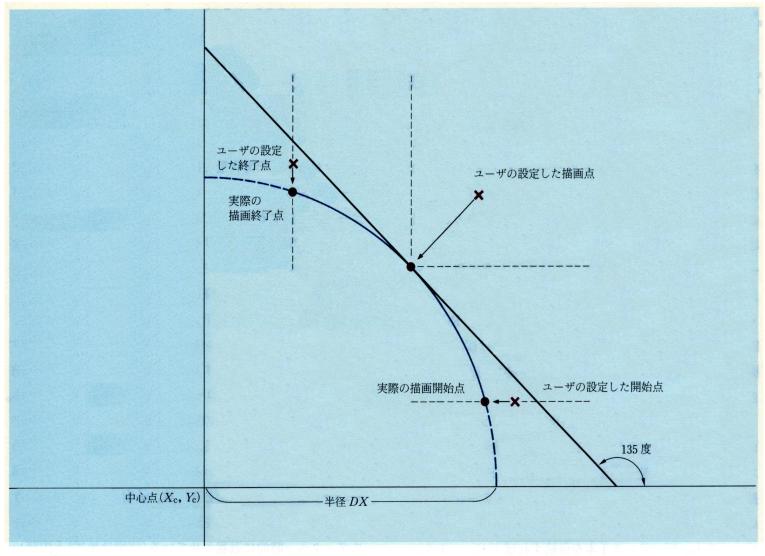

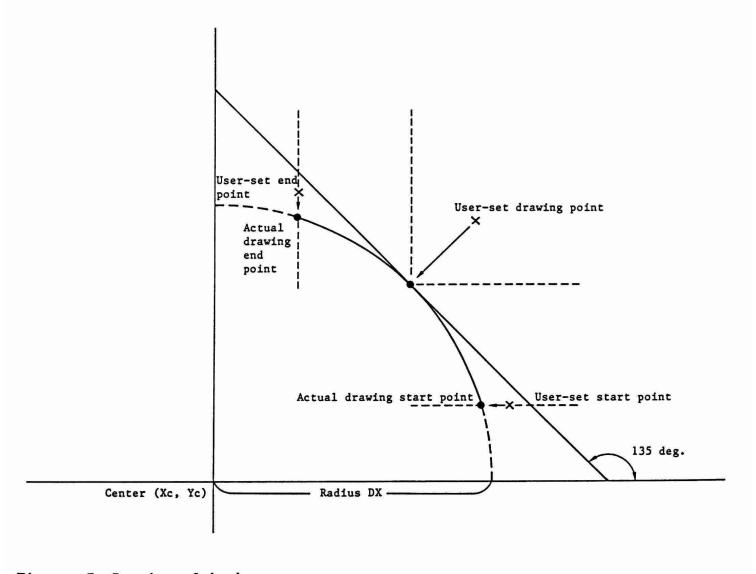

AGDCでは、円弧や楕円弧を描画する場合、開始点と終了点の座標で弧を定義する。一方、ビジネス・グラフィックスなどの応用では普通、角度で弧を定義する。このとき、座標を算出するための三角関数演算を簡略化すると、誤差のために実際に描画する弧には存在しない座標を指定してしまうことが起こる。AGDCではこのような設定がなされても座標に補正を加えて描画できるように考慮した。

第1象限に存在する弧を例に考えてみよう(図 5)。接線の傾きが135度より小さいときには、ユーザの設定した描画開始点が実際の弧の上に存在していなくとも、Y座標だけが一致していればよい。135度より大きいときには X座標だけが一致していればよい。135度のときには、Xと Y両方の座標を用いた大小比較(第1象限の場合は、描画位置がユーザの設定した位置より小さいかどうか)を判定している。この結果、座標をどの位置に設定したとしても描画の開始点または終了点を補正できる。このため、かなり乱暴な座標指定をしても暴走してしまうことはない。前述したプリプロセサ、描画プロセサの処理の流れでは、正確な座標値を③の処理によってプリプロセサが読み取っている。

#### ハードウエア・ウインドウは採用せず, 表示プロセサを単純に

描画プロセサ、プリプロセサ以外の部分を説明しよう。 AGDC では、GDC での応用実績をみて表示プロセサから 拡大表示機能や画面分割機能を削除した。これらの機能を 用いれば、表示アドレスの変更だけで高速に画面を分割したりスクロールできる。ところが、スクロール範囲や分割 方法は実装する表示メモリの大きさに依存してしまうなど、ソフトウエアの汎用性や機能に制約が生じる点が問題だった。ハードウエア・ウインドウ機能を搭載しなかった理由の一部もこの点にある。この結果、表示プロセサ部分は簡素化できた。マルチウインドウ表示は描画プロセサのコピー機能を用いて実現できる。また、表示プロセサはダイナミック RAM のリフレッシュ機能を備える。リフレッシュ・サイクル時には、13 ビットのリフレッシュ・アドレスを

AGDC では描画の開始点,終了点を指定することで弧を描画する。ユーザの指定した点が実際の弧の上に存在しない場合は,描 図5 弧の描画 画点を補正できる。

表示メモリ・アドレス出力の下位ビットに出力する。

同期信号発生器は、あらかじめユーザの設定したパラメ ータ値に従って水平/垂直の同期信号(HS/VS)や表示消去 信号(BLANK)などを出力する。また、表示メモリのアド レスに依存しないグラフィックス・カーソル表示用のタイ ミング出力(GCSR)をもつ。カーソルは表示画面の左上を 原点とした任意の位置に表示できる。カーソルの形状はク ロスヘアまたはブロックである。

CPU インタフェースは、システム・バスと AGDC 間の信 号授受のタイミングを制御する。CPU が表示メモリをアク セスするときに動作するアドレス拡張や表示メモリ・バス のアービトレーション機能も有する。

AGDC は CLK と SCLK と呼ぶ 2 系統のクロック入力 端子をもつ。同期信号発生器と表示プロセサには、SCLK から入力したクロックを供給している。SCLK の周波数は 使用するディスプレイ装置の仕様や表示分解能などに依存 して決まる。したがって、クロック周波数をコントローラ の最高動作周波数 (fmax) よりも低く設定しなければならな いことも起こり得る。その場合には、コントローラの備え る描画速度を100%発揮することはできない。そこで、 AGDC では、プリプロセサと描画プロセサには CLK とい う SCLK とは別系統のクロックを供給できるようにした。 この結果, プリプロセサと描画プロセサは常に最高動作周 波数で動作できる。

# デュアル・ポート・メモリなどで構成した 最大32Mバイトの表示メモリを制御できる

AGDC はシステム・バスから分離した表示メモリ・バスを直接制御する。24 ビットのワード・アドレス出力 (DA23~16 および DAD15~0)とその下位 16 ビット (DAD15~0) に入出力するデータ端子をもっている。表示メモリの容量は最大 32 M バイトで、1024×1024 ビットのメモリ・プレーン 256 枚に相当する。すべてのメモリを表示用フレーム・バッファとして割り当てなくてもよい。漢字フォント・パターンや動画用パターンを格納している ROM やRAM を表示メモリ領域の一部に実装しておけば、コピー機能を使って高速な文字フォント展開や動画制御などができる。

漢字フォント・メモリ(漢字 ROM)はライン方向のアドレス・カウンタなどを付加することなく,表示メモリ・バス上にそのまま実装できる。漢字 JIS コードは 14 ビット長である。また,16 ビットの表示メモリ・データ・バスに,たとえば  $32\times32$  ドットのデータを出力するには,行アドレス 5 本,列アドレス 1 本を供給すればよい。つまり,漢字コード用 14 ビット,フォント用 6 ビットの,計 20 ビットのワード・アドレスがあれば, $32\times32$  ドット構成の第1,第2 水準の漢字 ROM を実装できる (AGDC はワード・アドレス 24 ビット)。

バイト・アドレスが 20 本の 16 ビット CPU では、32×32 ドットの漢字 ROM を主記憶上に直接マップすることすらできない。システム・バス側に文字フォント・メモリを実装し、フォント・データをコントローラに転送するようなシステム構成を採ると、フォント・データの読み出しやその転送動作だけで多くの時間を浪費することになる。

#### 表示メモリを塗りつぶしパターンの格納や スタックとして使用

多くのコントローラでは、描画を実行するたびに、必要 とする塗りつぶしパターンや文字フォント・データなどを システム・バスから内蔵レジスタに設定する。ところが、 内蔵レジスタの記憶容量には上限があるため、描画途中で データの書き換えが必要となったり、複雑な塗りつぶしパ ターンを選択することができなかった。

AGDCでは、表示メモリを記憶容量の制約がほとんどないワーキング領域として使えるようにした。文字フォントや動画用のパターンと同様に、塗りつぶしパターンも塗りつぶしを実行する前に表示メモリにあらかじめ記憶させておく。塗りつぶしパターンを表示メモリ上に格納しておけば、そのパターンを転送する必要はない。主記憶上に格納した場合でもCPUのブロック転送命令一つで転送できる。

表示メモリはペイントの実行に必要なデータのスタック 領域としても使用している。塗りつぶす領域を決めるため に境界点検索を実行しているとする。この間に、ある一部 分の閉領域を特定できたときには、検索を中断してしまう のではなく、その閉領域を表現するために必要なデータを スタックへ一時的に退避させている(詳細は後述)。内蔵レ ジスタをデータ・スタックのために使用してもよいが、こ の場合にもレジスタの記憶容量の点からスタック・レベル の上限に制約が生じてくる。境界点検索のアルゴリズムに も依存するが、複雑な図形になるにつれてスタック・レベ ルがその上限を超える確率は高くなる。

表示メモリ内にワーキング領域を設定するには、その先頭絶対アドレスとその大きさを AGDC に与える。定義したスタック領域がオーバフローしたときには、動作を停止し描画プロセサ・エラーであることを CPU に知らせる。

#### CPU は表示メモリおよび AGDC の内部レジスタを 直接アクセスできる

CPU が表示メモリを主記憶と同等にアクセスするには、表示メモリを CPU のメモリ・アドレス上に主記憶の一部としてマップしなければならない。このため、AGDC は、

システム・バス (CPU) のバイト・アドレス 20本 (MA<sub>19~16</sub> と MAD<sub>15~0</sub>)を入力するアドレス端子と, CPU が表示メモ リをアクセスするときに低レベルにする端子(CSDM)と を備えている。

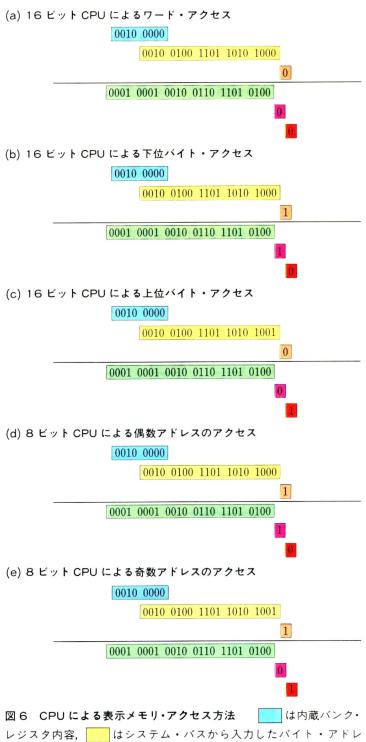

表示メモリ・バスのアドレスは24ビットのワード・アド レスである。CPU のバイト・アドレスを 24 ビットのワード ・アドレスに拡張するため AGDC 内に 8 ビットのバンク・ レジスタを設けた。図6にアドレス拡張方式を示す。バン ク・レジスタに20H (図では ) を設定しておき, 24DA8H または 24DA9H (図では \_\_\_\_) のバイト・アドレ スを与えたときの拡張例を示してある。 で示した表示 メモリ下位バイト・エネーブル信号(DLBE)はバイト・ア ドレス最下位ビットと等しい。システム側のデータ・バス 幅は8ビットでもかまわない。このときは, \_\_\_\_ で示した 上位バイト・エネーブル信号(UBE)を常に高レベルにし て使用する。

座標レジスタなどの AGDC の内部レジスタを CPU か らアクセスすることもできる。AGDC のパラメータ・レジ スタ類は、CPU のバイト・アドレス下位 8 ビットによって 選択できる。チップ・セレクト信号(CSIR)を低レベルに すると内蔵レジスタがアクセス可能になる。このように AGDC の制御下にある表示メモリと内蔵レジスタを CPU によって直接アドレスできるため, 汎用的なソフトウエア デバガを用いて簡単にそれらの内容をダンプしたり書き 換えたりできる。

#### バス・アービタを内蔵

こうしたマップ機能に関連して、表示メモリ・バスの使 用優先順位づけを制御するバス・アービタを内蔵している。 また、CPU に対してウエイト動作を要求するレディ信号 (READY) を出力する機能もある。したがって、タイミン グ設計が難しいバス・アービタを外部回路で構成する必要 はない。表示メモリ・バスの使用優先順位を高い順に並べ ると以下のようになる。

- ① AGDC による表示アドレスおよびリフレッシュ・アド レスの発生

- ②表示メモリ・バスの使用許可を受けた他のプロセサに

ス. はシステム・バスの上位バイト・アクセス時に低レベルとな ス. は表示メモリ・バスの上位バイト・アクセス時に低レベルと なる DUBE 信号, ■ は下位バイト・アクセス時に低レベルとなる DLBE 信号を示す。

16 ビットのデータ・バス幅をもつ CPU によるワード・アクセス. 下 位バイト・アクセス, 上位バイト・アクセス, および, 8 ビット CPU に よるバイト・アクセスに対応したアドレス拡張ができる。

よる表示メモリ・アクセス

- ③ AGDC を経由した CPU による表示メモリの直接アクセス

- ④ AGDC による描画アドレスの発生

AGDC は優先順位の高い表示アドレスの発生やリフレッシュ・アドレスの発生を行なう。このため、通常は表示メモリ・バスのバス・マスタとして動作する。表示メモリ・バスを外部のプロセサなどが使うことを考慮して、表示メモリ・バス使用権要求信号の入力端子(HLDRQ)を設けた。AGDC はこの信号を受け取ると表示メモリ・バス側のアドレスとデータ出力をフローティング状態にするとともに、描画を実行中である場合にはその描画を一時的に停止

させる。さらに、承認信号の出力端子(HLDAK)の立ち下がりによって要求受け付けを要求源に示す。また、AGDCによる表示やリフレッシュのためのアドレス供給は優先順位が一番高いので、HLDAKの立ち上がりによってバス使用権の返還を逆に要求する。

#### 4種類のアドレス・サイクルを用意

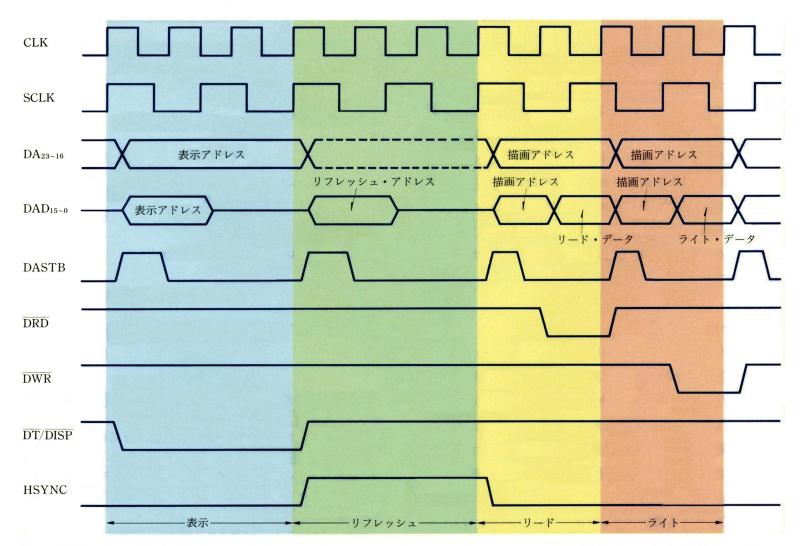

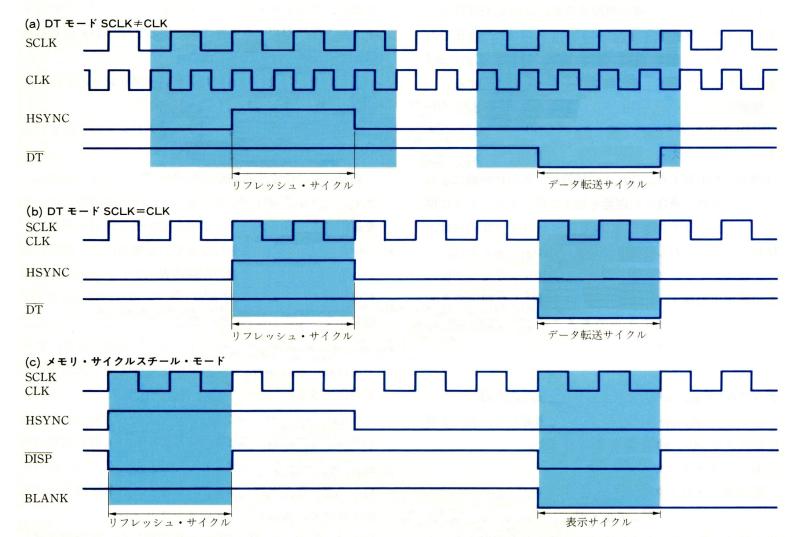

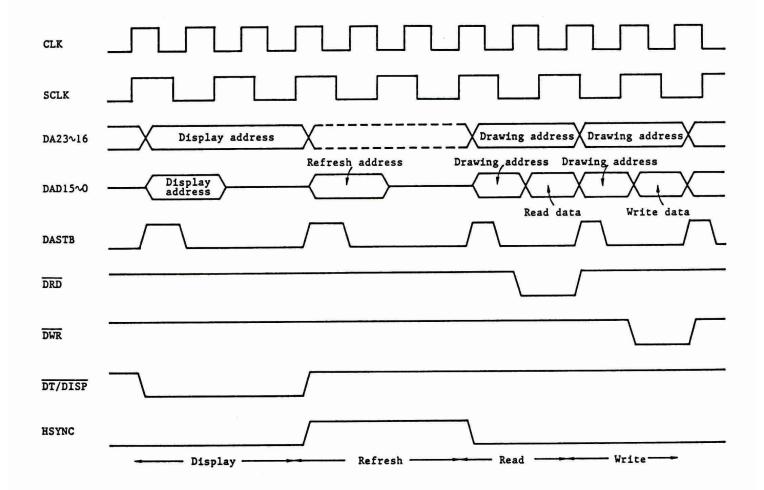

AGDC は次の 4 種類の表示メモリ・バス・アドレス・サイクルをもつ (**図 7**)。

- ① 描画アドレス・リード・サイクル

- ② 描画アドレス・ライト・サイクル

- ③表示アドレス・サイクル

図フ 表示メモリ・アドレス・サイクル 表示メモリをアクセスするときには、必ずアドレス・ストローブ信号(DASTB)を出力する。アドレス・ストローブ信号は、表示およびリフレッシュ時には SCLK に同期し、リードおよびライト・サイクル時には CLK に同期している。

#### ④ リフレッシュ・アドレス・サイクル

GDC の描画アドレス・サイクルは常にリード・モディフ ァイ・ライトを実行するため 4 クロックであった。AGDC では、描画サイクルは CLK に同期して 2 クロック、表示と リフレッシュ・サイクルは SCLK に同期して 2 クロックに してある。ダイナミック RAM に対するリフレッシュ動作 の実行を選択すると、水平同期期間にリフレッシュ・アド レス・サイクルを挿入する。描画アドレス・サイクルでは, 2 クロックごとに連続して読み出しや書き込み動作を実行 することもあれば、描画サイクルと次の描画サイクルとの 間に1クロック間の空き時間を挿入することもある。

各アドレス・サイクルの先頭では、必ずアドレス・スト ローブ信号(DASTB)を出力するので、外部回路はそのア ドレス・サイクルを正確に把握できる。この DASTB はア ドレス・データ多重化端子からアドレスだけを抜き出した り、ダイナミック RAM に供給する RAS 信号, CAS 信号 を生成するための基準タイミング信号として使用する。

描画アドレス・リード・サイクルでは、読み出し信号 (DRD) を出力するので、データ・バスの方向制御が行なえ る。描画アドレス・ライト・サイクルでは、書き込み信号 (DWR) を出力する。これらの信号は、外付け回路によっ て各々の装置に適合した遅延を加えた後,表示メモリに供 給する。表示サイクルとリフレッシュ・サイクル時には、 DASTB しか出力しない。表示サイクルであることは、デ ータ転送タイミング信号と表示サイクル・タイミング信号 との兼用出力端子(DT/DISP)の信号により判別できる。 リフレッシュ・サイクルであることは水平同期信号 (HSYNC) でわかる。

#### デュアル・ポート・メモリにデータ転送信号を出力

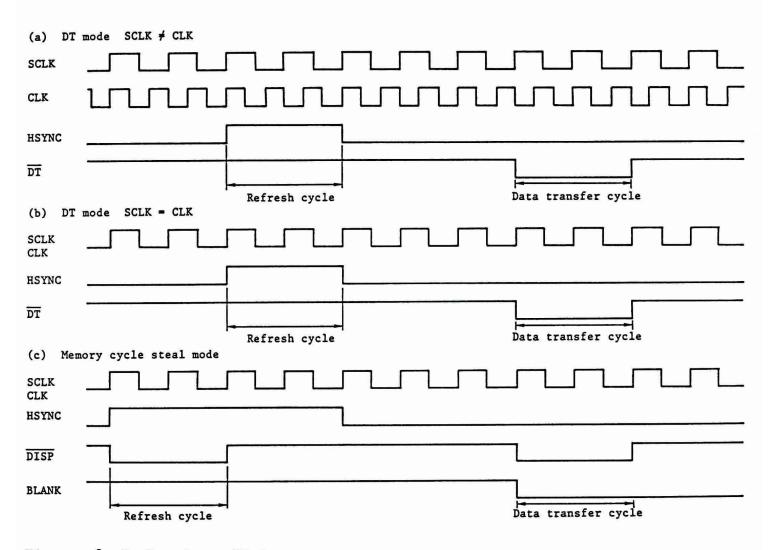

デュアル・ポート・メモリの使用を考慮して、次の2種 の描画タイミング動作モードを用意した。

- ① データ・トランスファ・モード

- ② メモリ・サイクル・スチール・モード

表示メモリとしてデュアル・ポート・メモリを使用する 場合には、データ・トランスファ・モードを選択する。こ のモードでは、異なった周波数のクロックを CLK 端子、

SCLK 端子に供給してもよい。ただし、異なるクロックに同 期した信号の同期をとるのに必要な同期化回路の構成から,

$f_{\text{max}}$ (最大動作周波数)  $\geq$  CLK  $\geq$  SCLK  $\geq$  CLK/2 の関係を満たさなければならない。この状態ではリフレッ シュ・サイクルとデータ転送サイクルには描画できない。 CLK を単位として, さらにその前 2 クロック, 後 1 クロッ クの間は描画できなくなる場合がある(図8(a))。

CLK と SCLK に同一のクロックを供給した場合には, フラグの設定によって、同期化回路をバイパスできる。こ の状態では、リフレッシュ・サイクルとデータ転送サイク ル以外のすべてのタイミングで描画を実行できる(図8 (b))

描画タイミング選択をデータ・トランスファ・モードに すると、デュアル・ポート・メモリに対してデータ転送タ イミング信号 ( $\overline{\mathrm{DT}}$ ) を出力する。次の 2 種の  $\overline{\mathrm{DT}}$  信号を発 生するタイミングが選択できる。

- ①1 走 存線の表示開始時および表示アドレスの下位8ビ ットがゼロになったとき。

- ②1画面表示の開始時および表示アドレスの下位8ビッ トがゼロになったとき。

表示メモリの水平方向を表示画面よりも大きく定義し, 水平方向へのスクロールを可能にした構成の場合には, ① を選択する。表示メモリの水平方向が表示画面と同じで, ノンインタレース走査を行なっている場合には, 画面に向 かって右端と次の走査線の左端の表示アドレスには連続性 が保たれているので ② を選択できる。 ② は ① よりも DT 信号発生の頻度が低いのでその分, 描画可能タイミングが 増加する。デュアル・ポート・メモリを使用すれば、ドッ ト周波数が数百 MHz となるような高解像度の表示装置に も対応できる。

表示画面が高解像度になるにつれ,単位時間当たりの表 示データの読み出し量は多くなる。このため、DT信号の発 生間隔を短くする必要が生じてくる。AGDCでは、高いク ロック周波数を維持しつつ低解像度から高解像度表示に対 応するため、表示アドレスのインクリメント形態を《1/4、 1/2, 1, 2, 4, 8, 16, 32》の8種用意した。概念的に言え ば、640×400ドットのノンインタレース表示であれば《1》 が適用できる。これよりも低解像度であれば小さい値,高 解像度になるにつれて大きな値を選択することになる。

#### メモリ・サイクル・スチールもできる

コストをできるだけ低く抑えたい場合やレーザ・プリンタのように表示を特に必要としない場合には、デュアル・ポート・メモリではなく通常のRAMを表示メモリとして使用することもできる。このため、メモリ・サイクル・スチール・モードを設けた。このモードでは、CLKとSCLKには同一信号源のクロックを供給しなければならない。

リフレッシュおよび表示期間中では、リフレッシュ・ア ドレス発生を含む表示サイクルと描画を実行できる描画サ イクルとを 2 クロックごとに交互に切り替えて発生させている (図 8(c))。このため、この期間での描画実行可能なタイミングは単位時間当たり 50% になる。表示期間以外では、リフレッシュ・サイクルを除きすべてのタイミングで描画を実行できるので、この値は少しだけ増える。ただし、メモリのサイクル時間の制約から解像度の上限が決定されるので、このサイクル・スチール・モードは比較的解像度の低い装置にしか適用できない。水平走査周波数が 24kHz の標準的なディスプレイを使用し、表示メモリのデータ・バス幅を 16 ビットとし、ダイナミック RAM のサイクル時間を 300 ns とすれば、640×400 ドットのノンインタレース表示あたりにその上限がくる。

図8 描画のできないタイミング 色で示す期間には描画は実行できない。クロック発生源の異なる DT モード (SCLK  $\pm$  CLK),同一のクロックを供給したときの DT モード (SCLK  $\pm$  CLK),サイクル・スチール・モードのときで描画できないタイミングは変化する。

# パラメータ直接転送方式の コマンド・インタフェースを採用

描画プロセサに高速描画機能をもたせても、 それをいか に効率良くシステム・レベルで生かせるかが重要である。 つまり、CPU とコントローラでコマンドを受け渡す手順 (コマンド・インタフェース) によって実際の性能は左右さ れる。われわれは開発の初期からこの方法を十分に検討し た。

コマンド・インタフェース法は全体像としてとらえると 次のように区分できる。

- ①システム・バス側でのデータ転送方法

- (a)パラメータ直接転送

- (b)パラメータ間接転送

- ② コントローラの状態検出方法

- (a) ステータス・フラグ

- (b)割り込み要求

- (c) ウエイト要求

- (d)DMA 要求

- (e)ホールド要求

- ③ 転送データの格納形式

- (a)間接アドレス指定

- (b)直接アドレス指定

- ④ 転送データの格納先

- (a) レジスタ

- (b) FIFO

AGDC は、①(a)、②(a)、(b)、(c)、③(b)、④(a)の組み 合わせを採ることにした。

パラメータ間接転送方式(①(b))はデータ生成時間が全 体の描画時間を引き延ばすため採用しなかった(後述)。こ の方式と密着した DMA 要求やホールド要求 (②(d), (e)) も除外した。転送データの格納形式に関しては、直接アド レス指定を採用した。間接アドレス指定は、コマンドとパ ラメータまたはアドレスとデータとを区別して転送データ を組み立てねばならない。また、アドレスとデータとを同 時に転送できる直接アドレス指定に比べて明らかに転送バ イト数が増加するためである。転送データの格納先はレジ スタにした。FIFO を用いても記憶容量に上限が生じる。ま た, あらためて読み出し動作が必要になるためである。

AGDC 内のレジスタは CPU のアドレス空間にマップさ れている。このため、CPU がコマンドを AGDC に与えるに は、主記憶に対する通常のデータ・ムーブ命令を実行する だけでよい(**図 9**)。図 9 で の部分が AGDC 内のパラ メータ RAM への書き込みに対応している。パラメータ RAM 内の 32 ワードのレジスタはそれぞれのアドレスに 対応して役割が決められている。プリプロセサはコマンド が書き込まれた時点で描画前処理を開始する。

状態検出方法は3種類用意した(②(a),(b),(c))。これ らの方法を描画種類によって切り替えながら使用してもよ い。パラメータ生成に専念できる専用の CPU と AGDC で システムを構成した場合,ウエイト要求(②(c))によるハ ードウエア・ハンドシェイクが最適である。CPU は AGDC に対する状態検出をする必要はなく、AGDC に対するアク セスを主記憶に対するアクセスと同等に扱える。しかし, CPUがウエイト状態のときには割り込み処理は実行でき ない。ステータス・フラグ(②(a))によるソフトウエア・ ハンドシェイクを選択すれば、コントローラがビジーのた めパラメータ類を転送できない状態で CPU がループして いたとしても割り込み処理は実行できる。

どのような状態検出方式を採った場合でも, ウエイト制 御信号 (READY) は CPU のウエイト制御を行なう端子に 接続しなければならない。READY 信号の発生期間は種々 の条件下において異なる。CPU が表示メモリをアクセスす る場合を例に採ると、読み出し時にはシステム・バスの読 み出し信号の立ち下がりからウエイト信号が5クロック期 間だけ発生する。書き込み時にはウエイト信号を発生しな

#### パラメータ間接転送方式には問題がある

パラメータ間接転送方式には、DMA 転送によってコマンド・パラメータを受け取る方法や主記憶上にあらかじめ作成しておいたコマンド・パラメータ・リストをコントローラ自身が読み取りにくい方法(リンクト・リスト)などがある。この方式では、座標列などの原型データから、コントローラに依存するコマンド・コードや転送アドレス情報などを含む転送データ列を生成する。このため、座標データを生成したらすぐに転送してしまうパラメータ直接転送方式に比べると、そのデータ生成処理が途中に入ることになる。その分、CPUの稼働時間は増え、パラメータ転送用のソフトウエアは複雑になる。

多数の直線描画で文字を描画するストローク文字描画のように、一連の描画処理の見通しが明瞭な場合には、コントローラの状態に依存して CPU の描画前処理を中断する

ことがない間接転送方式の利点を生かせるかもしれない。 しかし、DMA 転送方式では転送するデータ・ブロックの大きさをどのようにして最適化するかが大問題である。転送ブロックの大きさを固定することには基本的に無理がある。データがそろうまで転送できなくなってしまうからである。また、転送ブロックを細分化するにつれ、転送データの生成や DMA コントローラの動作設定などに要する処理時間は増加し、全体の描画速度は低下してしまう。

コントローラ自身がコマンド・リストを読みにいくリンクト・リスト方式ならば、このような問題は生じない。しかし、制御ソフトウエアは DMA 転送方式以上に複雑になる。作成済みのコマンド・パラメータ列や転送済みパラメータ列の認識、次のパラメータ列へのリンク、新しいパラメータ列の生成場所の定義などを CPU はすべて管理しなければならない。コントローラにそれらの情報を設定する

```

; 転送源アドレス・ピッチ転送: 2

CHAR: MOV WORD PTR PITCHS, 0002H

;水平方向ドット数転送:24

MOV WORD PTR DHH,

MOV WORD PTR DV.

: 垂直方向ドット数転送: 24

MOV WORD PTR EAD2H, 0000H

転送源上位ワード絶対アドレス転送:0

MOV AX, ES: WORD PTR BUF2

: 転送先 Y 座標初期值設定

MOV BX, ES: WORD PTR BUF3

; 転送先 X 座標初期值設定

MOV DI, ES: WORD PTR BUF1

; 色情報初期值設定

MOV DX, 0D000H

転送源下位ワード絶対アドレス初期値設定

MOV SI, ES: WORD PTR BUF8

コマンド・フラグ設定

CHAR 2: MOV CX, 041AH

ループ回数初期値設定: 26 文字 4 行

CHAR_1: MOV PLANES, DI

; 色情報転送

MOV EAD2L, DX

: 転送源下位ワード絶対アドレス転送

MOV X,

BX

; 転送先 X 座標転送

MOV Y.

AX

: 転送先 Y 座標転送

MOV WORD PTR COM, SI

コマンド・フラグ転送

ADD DX, +30H

文字コード変更

転送先 X 座標変更

ADD BX, +18H

INC

DI

色情報変更

AND DI, 0007H

DEC

CL

1行26文字描画終了?

CHAR_1

JNZ

SUB AX. 0018H

転送先 Y 座標変更

MOV BX, 0000H

転送先 X 座標変更

MOV CL, 1AH

文字ループ回数初期値設定

DEC CH

4 行文字描画終了?

CHAR_1

DEC

WORD PTR BUF7

26 文字 4 行描画×12 回終了?

JNZ

CHAR_2

```

図 9 24×24 ドット構成の文字 1280 字を展開するアセンブラ・プログラムの一部 CPU は 80286 である。コマンド・パラメータはこのようにムーブ命令 ( ) だけで簡単に設定できる。

必要もある。また、コントローラ自身がシステム・バスの使用権授受のためのホールド制御をすることになるため、インタフェースが可能な CPU をコントローラが限定してしまうことになりかねない。

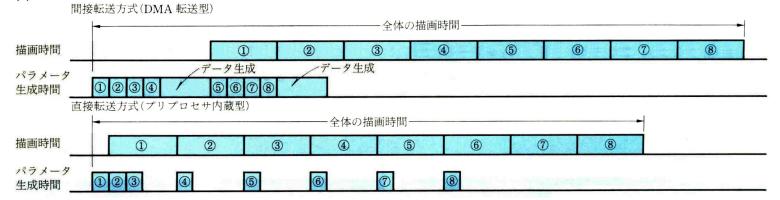

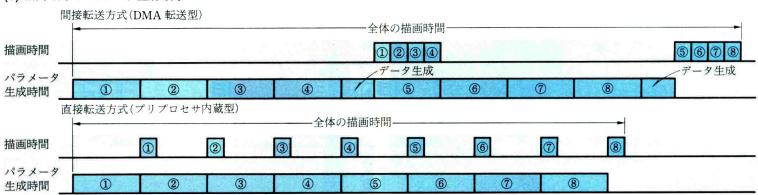

#### パラメータの生成時間と描画時間の関係が重要

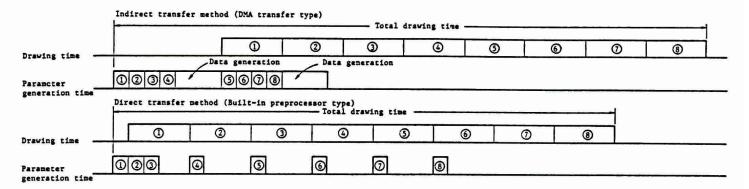

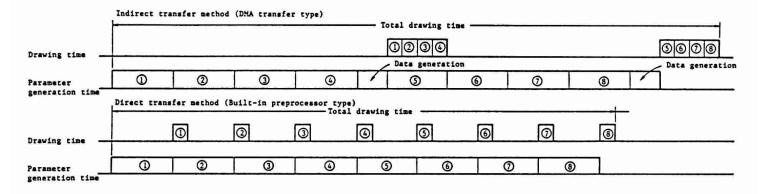

パラメータ間接転送方式は、CPUの処理を止めることなく、できるかぎり先のパラメータ生成まで実行をねらっている。ところが実使用状態では、パラメータ直接転送方式と比べて利点はないと判断した。これらを比較するうえで、CPUによるパラメータ生成時間とコントローラの描画時間との関連が重要な因子となる。

塗りつぶし描画のように描画時間がパラメータ生成時間 より遅い場合には、全体の描画時間は描画実行時間とほぼ 等しくなる。しかし、間接転送方式では第1回目のデータ 生成に要する時間だけ直接転送方式に比べ遅い (図 10 (a))。

1ドットしか描画を実行しない極端な例を採れば、全体の描画時間はパラメータ生成時間に依存することになる(図 10(b))。ところが、間接転送方式ではパラメータ列を前もって生成しておくので、パラメータ生成処理に依存することなく描画を連続的に実行できる。しかし、これはあらかじめ作成しておいたデータ・ブロックを用いた描画に限定される。直接転送方式では、パラメータ生成時間に依存しつつ描画を実行していくので連続描画はできないが、全体の描画は常に短い時間で終了する。

つまり、間接転送方式では、ブロック内の描画時間は直接転送方式のようにパラメータ生成時間に依存しないので 高速であるようにみえる。ところが、データ生成に費やす時間だけ実質的な全体の描画時間は長くなってしまう。

#### (a) 描画時間≧パラメータ生成時間

#### (b) 描画時間<パラメータ生成時間

図 10 実際の描画時間の比較 パラメータ直接転送方式と間接転送方式との間で、CPU とコントローラの動作を比較した。描画時間がパラメータ生成時間より長い場合(a) とその逆の場合(b) について全体の描画時間を評価している。パラメータ間接転送方式では、データ生成に要する時間だけ直接転送方式に比べ全体の描画時間は長くなる。

# 拡大・縮小,回転,塗りつぶしを 高速処理する描画プロセサ

複数の処理結果を同一画面上に表示したり,異なる文書の内容を参照しながら新しい文書作成をするなどの目的からマルチウインドウ機能を提供している表示装置は一般的になってきた。表示メモリの内容を転送せずに,表示アドレスを変更するだけでマルチウインドウ表示を実現したコントローラも登場している50。これをハードウエア・ウインドウ機能と呼ぶ。

ハードウエア・ウインドウはデータ転送を一切しなくてもすむので高速である。しかし、ビット境界をもつウインドウを表示するには、表示データをいったんチップ内部に取り込む必要がある。高解像度の表示装置では、数百 MHzにも達するドット周波数に対応した実時間制御をしなければならない。一般に、コントローラは、これより1 桁低い周波数での動作しか保証できないため、表示画面の解像度に制約が生じてくる。また、表示可能なウインドウの枚数にも上限がある。高解像度になるほどウインドウ枚数を増加したいのだが、逆に、より少ない枚数に抑えられてしまう。水平帰線期間内に、その表示ラインで発生するすべて

の表示アドレスの変化位置と先頭表示アドレスを転送しなければならないからである。ウインドウ内のスクロールは 高速になるが、これもまたウインドウ・メモリの容量に制 約されてしまう。

#### クリッピングをウインドウ表示, ピッキングに利用

高速さという利点はあるが、装置設計段階でかなり大きな制約の生じるハードウエア・ウインドウ機能は搭載しないことにした。コピー機能によって表示データを転送しウインドウを形成する。表示内容が固定したポップアップ・メニューと変化するウインドウとでは異なる制御方法を採る。ウインドウ制御ではフレーム・バッファと同じメモリ構成のウインドウ・メモリを必要とするが、メニュー表示用のデータは2次元的にもつ必要はない。メニュー表示の必要になった時点で、1次元の連続したアドレス上に置いた原型データを2次元的に展開するだけでよい。このため、1次元データを2次元展開したり、逆に、2次元データを1次元データに変換することを可能にした。

図 11 クリッピング例 クリッピング領域を指定し、内側(a)、外側(b)を塗りつぶすモードを指定し、四辺形内フィルを実行した。

マルチウインドウを効率的に形成するために,さらにハードウエア・クリッピング機能を用意した。対角座標を2点指定することにより四辺形のクリッピング領域を定義する。その内部だけを描画するか,外側だけを描画するか,クリップ動作をしないかの動作設定ができる(図11)。表示最前部に位置するウインドウには有効に利用できる。ペイントのときには,このクリッピング領域の定義を境界点検索領域の外枠指定として使う。

クリッピングを用いると画面上に描画してある図形を特定し、抜き出すピック動作が可能になる。コントローラに描画をすべて任せてしまうと、CPUは描画位置をトレースしていない限り、ピッキングはできない。そこで、AGDCにこの機能をもたせた。マウスやタブレットによってクリッピング領域をあらかじめ目的の位置に移動させておき、2×2ドット程度の狭い領域を定義する。描画領域をクリッピング領域の外側に設定し、表示結果が変化しないような論理演算モードを選択して描画を再実行させる。クリッピ

ングの発生したことを割り込みやフラグによって CPU は 知ることができ、そのときに描画していた図形をピックで きる。

#### プレーン型、ピクセル型の表示メモリを構成できる

AGDC の備える主な描画機能は表 1 に示した。しかし,そのすべての組み合わせが成立するわけではない(表 2)。軸が X 軸や Y 軸に平行ではない楕円の描画のように,AGDC が内蔵していない機能は CPU のソフトウエア処理によって補完しなければならない。このため,クリッピングのような AGDC の実行する機能を他の描画で使用しているならば,CPU による楕円描画にも適用できることが望ましい。この場合には,相対位置指定ができるドット描画を用いて,CPU で楕円を描画すればよい。表示メモリのうち,表示画面に対応するフレーム・バッファへの描画では,X-Y 座標による位置指定ができる。漢字 X-Y を標による位置指定ができる。漢字 X-Y を標による位置指定ができる。漢字 X-Y を標による位置指定ができる。漢字 X-Y を標による位置指定ができる。

表2 実際に使える描画機能の組み合わせ

|       |         | ピクセル構成 | ハードウエア・<br>クリッピング | 拡大・縮小 | 線種の選択 | 塗りつぶし<br>パターンの<br>選択 | 転送先(描画先)<br>位置指定 | 転送源(線種・塗りつぶしパ<br>ターン)位置指定 |

|-------|---------|--------|-------------------|-------|-------|----------------------|------------------|---------------------------|

| ドット   |         | 0      | 0                 | ×     | 0     |                      | 座標               | 内蔵レジスタ                    |

| 直線    |         | 0      | 0                 | 拡大のみ  | 0     |                      | 座標               | 内蔵レジスタ                    |

| 四辺形   |         | 0      | 0                 | 拡大のみ  | 0     |                      | 座標               | 内蔵レジスタ                    |

| 円·円弧  |         | 0      | 0                 | ×     | 0     |                      | 座標               | 内蔵レジスタ                    |

| 楕円・楕円 | <b></b> | 0      | 0                 | ×     | 0     |                      | 座標               | 内蔵レジスタ                    |

| ペイント  |         | ×      | 0                 |       |       | 0                    | 座標               | 内蔵レジスタ・先頭アドレス             |

|       | 四辺形内    | 0      | 0                 |       |       | 0                    | 座標・絶対アドレス        | 内蔵レジスタ・先頭アドレス             |

| 7 . 1 | 円内      | ×      | 0                 |       |       | 0                    | 座標               | 内蔵レジスタ・先頭アドレス             |

| フィル   | 台形内     | ×      | 0                 |       |       | 0                    | 座標               | 内蔵レジスタ・先頭アドレス             |

|       | 三角形内    | ×      | 0                 |       |       | 0                    | 座標               | 内蔵レジスタ・先頭アドレス             |

|       | 通常      | 0      | 0                 | 0     |       |                      | 座標・絶対アドレス        | 座標・絶対アドレス                 |

| コピー   | 90度回転   | ×      | 0                 | ×     |       |                      | 座標・絶対アドレス        | 座標・絶対アドレス                 |

| 76-   | 傾斜      | ×      | 0                 | ×     |       |                      | 座標・絶対アドレス        | 座標・絶対アドレス                 |

|       | 任意角回転   | ×      | 0                 | 0     |       |                      | 座標・絶対アドレス        | 座標・絶対アドレス                 |

| プット・  | 通常      | 0      | 0                 | ×     |       | ~ —                  | 座標・絶対アドレス        | _                         |

| ゲット   | 90度回転   | ×      | 0                 | ×     |       |                      |                  | 座標・絶対アドレス                 |

| CPU直接 | 描画      | 0      | ×                 | ×     |       |                      | 座標アドレス           | 任意                        |

置指定を使える。

色情報を記憶するには次の2種の方法がある。

- ① カラー・プレーン型

- ②パックト・ピクセル型

プレーン型では、1ピクセルの色情報を色プレーンの大きさだけ離れたアドレスにまたがって格納している。したがって、直線描画のように1ピクセルごとに描画する場合は、1ドットずつすべてのプレーンに対する描画を順次実行しなければならない。ところがプレーン型は隣接するビット列を一括して処理したほうが高速になるコピー、塗りつぶし、回転、拡大や縮小処理に適している。パックト・ピクセル型は、表示メモリをアクセスする最小単位(1ワード)にピクセル情報をすべて詰め込んでいるので、1ピクセルを同時に描画できる。1ピクセルを単位として描画していく図形描画では、プレーン型よりも高速である。しかし、1ピクセルを構成するドット数を変更すると、描画処理の流れや描画マスク回路などのハードウエアが大きく変わるので拡張性に欠ける。

AGDCでは、プレーン型の表示メモリに対してはすべての描画機能を適用できる。しかし、ピクセル型の得意とする図形描画については、ピクセル型の表示メモリにも対応できるようにした。このプレーンとピクセルのモード選択は描画時に動的に切り替えることができるので、プレーン型とピクセル型の2種の構成をもつ表示メモリを実装し、それぞれの特徴を生かすことも可能である。

GDC とは異なり、プレーン型であっても一つの描画コマンドの発行によってカラーの描画を実行する。図形描画や塗りつぶしでは描画先にある複数プレーンに対して、最大2種類の論理演算を指定できる。たとえば、4面のメモリ・プレーンに対し、2面ごとに別々の論理演算を実行できることになる。コピーやプット/ゲットでは同様の処理を転送源および転送先に対して実行できる。

ドット・マトリクス型のカラー・プリンタにカラー画面の ハードコピーを打ち出すことは容易である。複数のプレー ンに格納してある転送源データ間で各インク・リボンに適 応した論理演算を施し、90度回転したデータをシステム・ バスに読み出す90度回転ゲット・コマンドを1回発行すれ ばよい。これで縦方向 16 ドット 1 行分の印字ヘッド・ピン を直接駆動するドット列を AGDC から取り出すことができる。

#### 16/N 倍拡大, N/16 倍縮小が可能

拡大・縮小コピー時の倍率は、拡大時 16/N 倍、縮小時 N/16 (N は 1 から 16 の整数) とした。等倍近辺の倍率き ざみを多く取れるので実用的である。拡大・縮小の倍率に 制約をつけたのは、簡単なハードウエアによって高速な拡大・縮小コピーを実現するためである。たとえば 15/16 倍の縮小を考えてみよう。表示メモリから読み出した 16 ビットのうち、あらかじめ決められた 1 ビットを間引くだけで よい。縮小の場合、縮小率によってどのビットを間引くか はあらかじめ決定しておける。

縮小したデータはシフト、マスクなどの処理を通して再び表示メモリに書き込む。最終ワードの場合、拡大・縮小の終了していないビット数が16ビットあるとは限らない。このような処理では描画マスク演算をすることは難しい。AGDCでは、そのときの倍率と描画の終了していないビット数を基に、あらかじめマスクの形式を記入したテーブルを参照することによりマスクを生成している。

垂直方向の拡大・縮小は処理速度に敏感ではないので、 ソフトウエアによる計数処理をしている。2倍なら単純に 同じラインを2度描画するように拡大し、縮小ならば単純 に間引く。文字や図形を扱うグラフィックスでは、1本の線 が抜けたり、間隔がなくなると、視覚を通した情報量が激 減してしまうことがある。罫線が消えてしまわないように 直線描画するなど、縮小後のデータに対し応用に合わせた なんらかの補完処理をする必要があると思っている。

塗りつぶしパターンの参照方法として,次の3種類を用意した。

- ①内蔵レジスタ参照

- ② 表示メモリ参照

- (a) すべてのプレーンに共通なパターンを参照

- (b) 各プレーンに独立のパターンを参照

- ① はいわゆるベタ・パターンである。垂直方向やプレーン方向へは同じパターンの繰り返しになる。画面のクリア

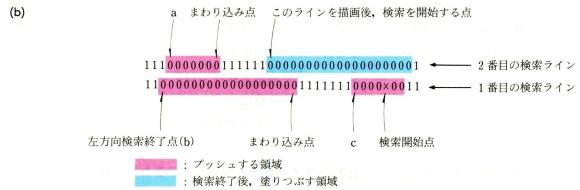

#### (b) ワード内境界点判定 (a) 検索開始点の"1", "O" 判定 MSB LSB **MSB** LSB MSB LSB LSB **MSB** 検索データ 検索データ 000000000000 ×××××100000××××× 0000000001111111 マスク・データ 000000000111111 1111111111111111 マスク・データ 1111111111111111 ××××10000000000 結果 0000000000100000 00000000000000000 結果 00000000000000000 境界点あり 境界点なし 境界点あり 境界点なし

検索データにマスクをかけた結果に対し、そのワード内に境界点が存在するか、存在すればそのドット位置はどこかを知 図 12 境界点の判定 ることができる。図中の"×"は任意の値("0"または"1")を示す。

に使うことが多いだろう。②(b)の参照方法を用いると,水 平、垂直、プレーン方向にすべて異なるパターンを参照で きるので、1ドットごとに異なる色彩を着けた塗りつぶし (タイリング) が可能となる。塗りつぶすラインの Y 座標 に依存して塗りつぶしパターンの参照位置の初期値算出や 変更をする機能を内蔵している。

#### 境界点検索を高速にすればペイントは速くなる

同じ大きさの領域を塗りつぶすならば、フィルのほうが ペイントより速い。フィルを実行するための座標は高速に 発生できる。一方、ペイントでは塗りつぶし領域を特定す るために、表示メモリの内容を読み出し、境界点を検索す る複雑な作業を伴うからである。ペイントの速度を上げる には,この境界点検索を短時間で終了させることが最優先 課題となる。新規に開発した境界点検索器は16ビットの検 索データを与えた直後に、次の情報を描画プロセサに返す ことができる。

- ① 境界点が存在するかどうか

- ② 存在する場合には、そのドット位置

境界点がその検索データ内に存在していなければ,次の 隣接したワードの内容を読み、そこから検索データを作る。 カラー表示の場合には、境界点は境界色として与えられる。 プレーンが3枚ならば、三つのプレーンのデータを連続し てプレーン当たり2クロックのうちに読み取りながら,境

界色指定にしたがってプレーン間でデータの論理演算を実 行し、検索データを生成している。すべてのプレーンに対 する読み出しが終了した時点で、16ピクセル(1ワード)の 検索データの生成が終了する。

検索データに対しては、検索対象とする領域を特定する ためにマスクをかけることができる(図12)。図12ではマ スク・データが"0"のビットのみ検索対象としている。検 索開始点そのものが境界に含まれているかどうかを判定す るには、検索開始点のデータだけを取り出せるようにマス ク・データを与える (同図(a))。その結果が"0" ならば境 界点はそのワード内に存在しない。ワード内のある1点か ら左右どちらかの方向への検索を続行していく場合には, 検索が終了した部分を再び検索対象領域としてしまわない ために、その点からワード境界までの間の検索データにマ スクをかける(同図(b))。ワード内に境界点が多数存在す る場合には,同じ検索データに対してマスクを変えるだけ ですむ。境界点検索器の出力する位置データは塗りつぶし 領域の大きさを算出するためだけでなく, そのワード内で の検索マスク・データを生成するためにも使っている。

#### 上下 2 ラインを読み取り領域のまわり込み点を抽出

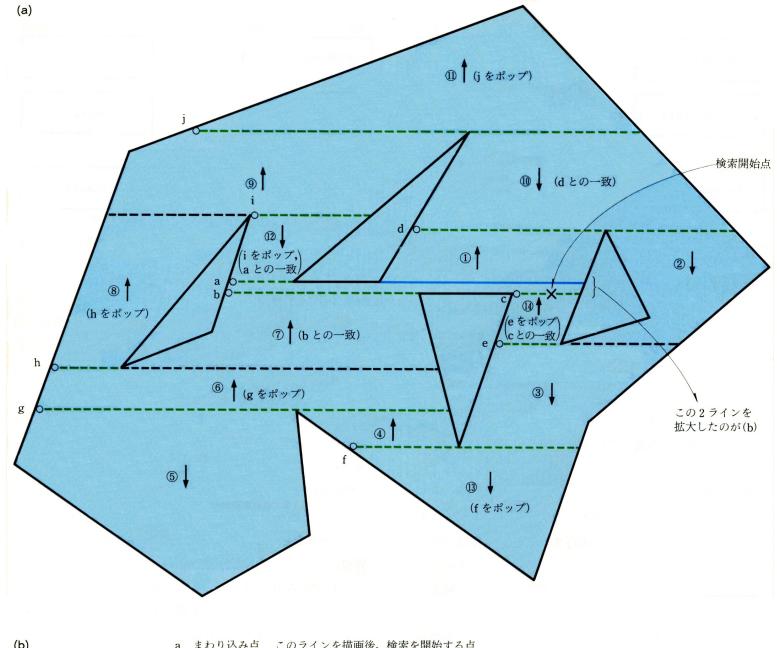

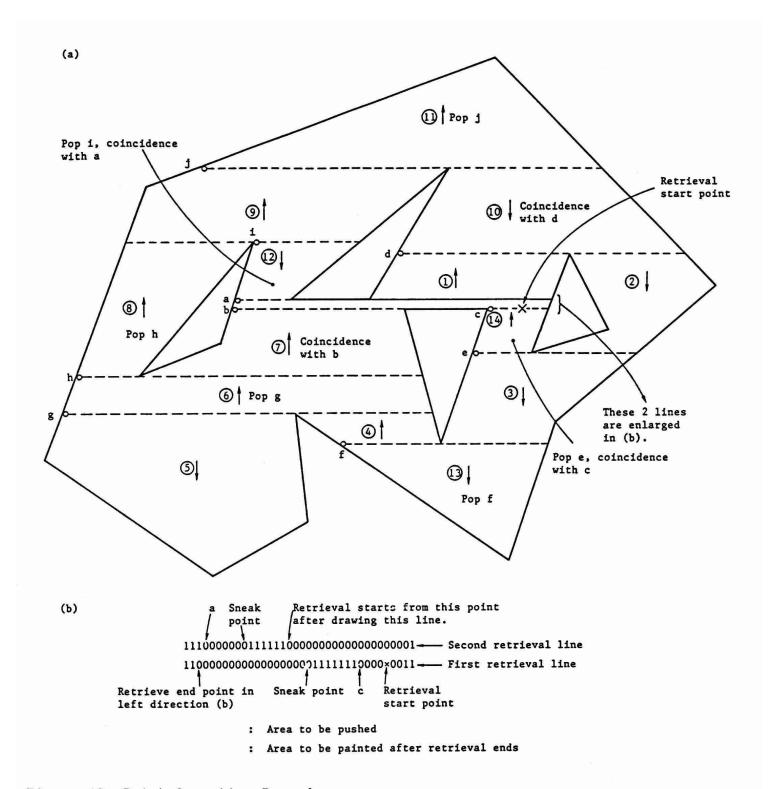

閉領域の塗りつぶし順序と境界領域データのプッシュや ポップの様子を図13(a)に示した。×印から検索を開始 し、①~⑩の順に塗りつぶしていく例である。まわり込み

図 13 ペイントの動作手順 任意の閉領域は、複数の領域に分割して塗りつぶす(a)。図では、①~⑭までを、矢印の方向に塗りつぶしている。(a)の一部を拡大し、(b)に示した。境界点検索の手順を示している。境界点検索処理は "0" から "1" または "1" から "0" への変化点の検索を基にした閉領域の特定、まわり込み点の抽出、検索終了判定、閉領域情報のプッシュやポップ、実際の閉領域内塗りつぶしを含む。

点の発生により、閉領域を14個の領域に分割した。①など の横に付けた矢印は塗りつぶしを実行していく方向を示し ている。

境界点検索を含む塗りつぶしは次のように進む。図中に 示した検索開始点から検索を始めるとしよう。検索開始点 を含むラインと、その上のラインを同時に検索する。1ライ ンの検索途中で左右の境界点を見つけたときには、その部 分の情報(閉領域情報)をスタックにプッシュする。この 例では, a, b, c をプッシュすることになる。① では図中 の から塗りつぶしを実行し、さらに上のラインの検索 へ移る。① の検索の最後では、② へのまわり込み点が発生 するので d をプッシュし、② の塗りつぶしを始める。この ように、塗りつぶしを実行しながら、閉領域情報を表示メ モリ上に置いたスタックに積んでいく。

⑤ の塗りつぶしが終了した時点では a~g がスタックに プッシュされている。⑥の領域では,スタックをポップ し、④の検索の終わりでプッシュしたgから検索、塗りつ ぶしを始める。また,⑥ ではその後 h をプッシュすること になる。

検索後の塗りつぶしを実行するときには常に, その検索 で特定した閉領域情報とスタックの内容との一致を調べて いる。⑦ の塗りつぶしでは、b との一致がとれたので、b の 閉領域情報にフラグを立て、ポップ後の検索を再びしない ようにしている。

境界点検索では、上下2ライン分の表示メモリ内容を交 互に読み取る方法を採った。この方法を使うと、塗りつぶ し領域にあるまわり込み点の抽出,検索途中で領域が確定 したときのスタック動作、および、検索終了の判定などの 境界点検索処理の流れ"を明瞭にできる。2 ライン分のデ ータを読み、それぞれの境界点検索結果を比較しながら境 界点を検索していく。検索途中で塗りつぶし領域が確定で きたときは、前述したようにあらかじめ定義しておいた表 示メモリ上のスタック領域に位置や領域の大きさなどを含 む6ワードの情報をプッシュする。

図13(b)に同図(a)の一部を拡大した。この図でもう少し 詳しい動作を説明しよう。

まず、検索開始点そのものが境界に含まれていないこと

を確認し、その後"0"から"1"への変化点を検索する。 その結果、点 c が得られる。次に c より 1 ラインだけ上の 点の境界点判定をする。その点が"1"なら左方向の境界が 見つかったことになるので、右方向へ検索していく。この 例では、"0"なのでまず左方向へ検索することになる。左 方向検索を開始するときには1番目の検索ラインでは"1" から"0"、2番目の検索ラインでは"0"から"1"へ変化す る点を検索する。

一般に, "0" から"1" への変化点が境界点となり, その 上または下の点が"1"であれば検索終了点となる。"0"で あればまわり込みの可能性がある。したがって、さらに"1" から"0"へ変化する点の検索をする。この処理を検索終了 点が見つかるまで続ける。

左方向の検索終了点 b を見つけ出すと、右方向への検索 を始める。このとき,検索途中で a と b の閉領域情報はす でにプッシュしてある。右方向検索では,まず c の閉領域 が確定するのでプッシュする。右方向検索が終了した時点 で塗りつぶしを実行するラインが決まる。このラインの左 端の点を検索開始点として①の残りの領域に対する検索 を始める。

#### バッファ・レジスタを利用し 90 度回転などを実行

90 度回転コピーを高速化するために 16 ワードのバッフ ァ・レジスタを内蔵した。このバッファは、そのアドレス バスとデータ・バス接続の制御によって、行方向から書 き込んだデータを、あたかも列方向から読み出すこともで きる構造をもっている。さらに, 転送源と転送先の転送領 域のビット位置の相対関係を判断して,バッファへのデー タ転送に無駄が生じない流れ制御も採用した。このバッフ ァ・レジスタは、ゲット/プット時には転送データを一時的 に記憶する FIFO としても機能する。

拡大・縮小を伴った任意角回転コピーは直線描画によっ て実行している。一般に, 図形を回転させると, 図形描画 領域内に描画をしない点が発生する。軸に対する回転角度 が45度になると、この現象は最も顕著になる。このような 特異点を判別して, 隣接する点への描画を, この特異点に 対しても同様に実行するかを選択できる。

### 実際の実行速度を 各種ベンチマーク・テストで評価

グラフィックス・コントローラの描画速度評価の方法は 各社各様である。評価環境の条件も明確でないことが多い。 したがって, 単純にそれらの値から描画速度を比較するこ とは難しい。コントローラの性能を「1ドット当たり何ナノ 秒」とか「1秒で何ベクトル」と表現することがあるが、こ れはいわば最大瞬間風速的な値である。描画のために表示 メモリを占有できる時間比率やコマンド・インタフェース などのシステム的要因は考慮していない。実際の描画速度 とは大幅に異なってくる場合も多い。

装置設計者がコントローラ採用の可否を判断する材料と して有用な数値はシステムとして組み上げたときの描画速 度であろう。そのためには、直線を1本だけ描画したり24 ×24ドットの文字を1文字だけ描画したときに要した時 間を基に1秒間に描画できる直線の本数や文字数を算出す る方法も良くない。描画を連続的に実行した場合に, 描画 と描画との間隔がどの程度あいてしまうのかについて評価 していないことになるからである。

表3 描画サイクル数 この値だけを基にして、全体の描画速度を 算出してしまうのは良くない。塗りつぶしでは参照パターンの違いに よって、サイクル数が異なるが、塗りつぶし全体の描画速度はほとん ど変わらない。

| 描画内容                                                             | 描画サイクル数                                |

|------------------------------------------------------------------|----------------------------------------|

| 直線                                                               | 4クロック/ドット<br>(ピクセル)                    |

| 四辺形のうちの水平直線 (プレーン構成)                                             | 4クロック/ワード                              |

| 円, 楕円                                                            | 6クロック/ドット<br>(ピクセル)                    |

| コピー<br>データ置き換えのみ<br>論理演算実行                                       | 2クロック/ワード<br>4クロック/ワード                 |

| 塗りつぶし<br>内蔵レジスタ参照、データ置き換えのみ<br>内蔵レジスタ参照、論理演算実行<br>表示メモリ参照、論理演算実行 | 2 クロック/ワード<br>4 クロック/ワード<br>6 クロック/ワード |

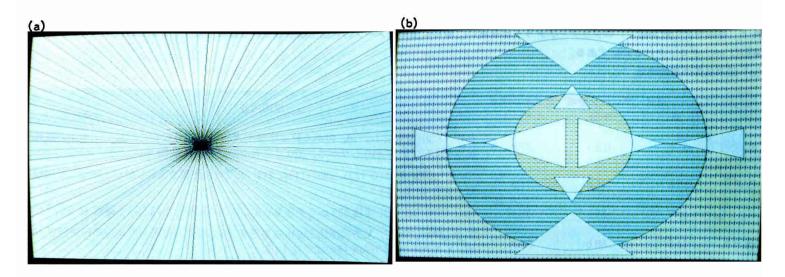

われわれは、図形やグラフィックス文字描画の場合には, 同一種類の描画を連続的に実行したときの総合的な描画速 度を評価することにした。 あらかじめ, 座標値を与えてお き、CPU が描画前処理を開始した時点から最後の描画が終 了するまでの時間をロジック・アナライザを用いて実測し た。パラメータ間接転送方式によるコントローラの場合に は、DMA 転送データやコマンド・リストの作成処理も含め た時間として表現することになる。CPUのデータ転送速度 に依存してしまうゲットおよびプットは除外した。表示メ モリとしてデュアル・ポート・メモリを使用しているが、 そのリフレッシュのために6%が消費されたため、93.7%の描画可能タイミングが確保されている。

#### 理論的には 2~6 クロックで 1 ワードを処理

実測値の前に、描画実行に必要なクロック数(理論値)を 表3に示す。直線はGDCと同一のクロック数で描画する が、円、楕円はむしろ遅い。これは、楕円の描画アルゴリ ズムを基に円を描画していること,一つのコマンドによっ て円全体を描画できるようにしたことによる。プレーン構 成を採る表示メモリに対し、四辺形を描画するときには、 水平線の部分は16ドットを1回の描画サイクルで描画で きる。転送源と転送先をともにビット境界で指定できるコ ピーを, 転送源または転送先に対する論理演算を実行しつ つ、1ワード当たり6クロックで実行する。転送先の既存デ ータを無視し, すべて転送源データで置き換える設定をす ると、1ワードのコピーは4クロックで終了する。

塗りつぶしでは、内蔵レジスタに格納してある塗りつぶ しパターンを参照する場合と、表示メモリ上のパターンを 参照する場合とで実行サイクルが変わる。表示メモリ上の パターンを参照するには、読み出しサイクル 2 クロック分 だけ、内部レジスタを参照した場合に比べて時間がかかる。 四辺形内塗りつぶしでは、コピーの場合と同様に、データ

表 4 描画時間の計測値 ロジック・アナライザを用い,最初に描画パラメータの発生を指示してから描画を終了するまでの実行時間を実測した。 単位は ms, クロックは 8 MHz である。

#### (a) 図形描画の描画時間

|      | プレーン構成<br>1 面 | プレーン構成<br>3 面 | ピクセル構成<br>4 ビット | 描画内容                                                                                                           |

|------|---------------|---------------|-----------------|----------------------------------------------------------------------------------------------------------------|

| 直線   | 37.8          | 113.4         | 37.8            | (319, 239) を始点とし、(0, 0)から終点座標を $X$ 方向 $\pm 10$ しながら、240ピクセルの直線総数 128本、 $Y$ 方向 $\pm 10$ しながら、320ピクセルの直線を総数 96本。 |

| 四辺形  | 15.6          | 46.8          | 37.8            | (0, 0)-(639, 479) から (235, 235)-(404, 244) まで対角座標を±5 しながら描画した四辺形を総数 48 個。                                      |

| 円    | 30.0          | 69.0          | 30.0            | 中心 (319, 239) 固定, 半径 239 から半径を-5 しながら描画した同心円を総数 46 個。                                                          |

| 楕円1  | 34.8          | 80.6          | 34.8            | 中心 (319, 239) 固定, $X$ 方向半径 239 から半径を $-5$ しながら描画した同心楕円を総数 46 個。 $X$ 方向半径と $Y$ 方向半径の比率は $4:3$ 。                 |

| 楕円 2 | 45.0          | 104.2         | 49.8            | 楕円 $1$ の条件のうち、 $X$ 方向半径と $Y$ 方向半径の比率を $3:4$ とした同心楕円。                                                           |

#### (b) 塗りつぶし描画の描画時間

|          | ベタパターン | タイリング 1 | タイリング2 | 描画内容                                                                                             |

|----------|--------|---------|--------|--------------------------------------------------------------------------------------------------|

| 画面クリア    | 28.8   |         |        | 640×480ドット×3面×2組(11万5200ワード)に対するクリア。                                                             |

| 四辺形内フィル  | 7.1    | 13.5    | 13.8   | 400×300の矩形領域に対する論理演算付き塗りつぶし。                                                                     |

| 円内フィル    | 9.3    | 9.3     | 9.3    | 半径 150 ドットの円形領域に対する論理演算付き塗りつぶし。                                                                  |

| 楕円内フィル 1 | 6.7    | 6.7     | 6.7    | X方向半径 $150$ ドット, $X$ 方向半径と $Y$ 方向半径 の比率は $4:3$ の楕円形領域 に対する論理演算付き塗りつぶし。                           |

| 楕円内フィル2  | 12.3   | 12.3    | 12.3   | X方向 半径 $150$ ドット, $X$ 方向半径と $Y$ 方向半径の比率は $3:4$ の楕円形領域に対する論理演算付き塗りつぶし。                            |

| 三角形内フィル  | 3.0    | 3.0     | 3.0    | (152, 419)-(320, 240)-(459, 320) の 3 点で囲まれる三角形領域に対する論理演算付き塗りつぶし。                                 |

| 台形内フィル   | 5.2    | 5.2     | 5.2    | (0, 150)-(300, 150)-(30, 0)-(270, 0) の 4 点で囲まれる台形領域に対する論理<br>演算付き塗りつぶし。                          |

| ペイント     | 94.5   | 96.7    | 97.8   | 中心 (320, 240) で半径 100 と 220 の円, (0, 0)-(639, 479) の四辺形, 8 個の三角<br>形で形成する 3 個の閉領域に対する任意閉領域内塗りつぶし。 |

#### (c)コピーの描画時間

|                   | 1面→1面 | 3面→1面 | 1面→3面 | 3面→3面 | 描画内容                                                                             |

|-------------------|-------|-------|-------|-------|----------------------------------------------------------------------------------|

| 通常コピー1            | 12.0  | 29.2  | 24.3  | 36.3  | 640×480ドットの矩形領域の論理演算なしでの転送。                                                      |

| 通常コピー2            | 18.0  | 29.2  | 40.5  | 52.1  | 640×480ドットの矩形領域の論理演算付きでの転送。                                                      |

| 90 度回転コピー         | 20.2  | 29.2  | 43.1  | 61.1  | $480 \times 640$ ドットの矩形領域の論理演算付きでの $90$ 度回転をともなった転送。                             |

| 拡大コピー             | 34.1  |       | 56.6  | 102.3 | $16/13$ 倍に拡大したデータを $640 \times 480$ ドットの転送先矩形領域に対して、論理演算付きで転送。                   |

| 縮小コピー             | 63.3  |       | 95.6  | 153.0 | $640 \times 480$ ドットのデータを $13/16$ 倍に縮小して論理演算付きで転送。                               |

| 任意角回転<br>拡大・縮小コピー | 35.2  |       | 71.6  | 103.1 | $200 \times 200$ ドットのデータを $14/16$ 倍に縮小し、 $X$ 、 $Y$ 軸に対し $\pi/8$ だけ回転して論理演算付きで転送。 |

|            | 1面→1面 | 1面→3面 | 描画内容                          |

|------------|-------|-------|-------------------------------|

| 文字フォント通常展開 | 91.5  | 155.2 | 24×24 ドット構成のフォント 1248 字を通常展開。 |

| 文字フォント傾斜展開 | 119.2 | 196.5 | 24×24 ドット構成のフォント 1248 字を傾斜展開。 |

図 14 描画時間の計測に用いたベンチマークの処理例 (a) は直線(表 4(a)), (b) はペイント(表 4(b)) の描画例である。

の置き換えだけの設定をすると 2 クロックで 16 ビットを 塗りつぶせる。

#### 任意閉領域内の塗りつぶしは特に高速

図形の描画,塗りつぶし,コピーの実行時間を**表4**の (a), (b), (c)にそれぞれ示した。

1面の表示メモリ・プレーンのみに対する描画時間と3面(8色表示)に対する描画時間を比べると,直線(図14(a))の場合には3倍になっている。しかし,円,楕円では2倍強にしかならない(表4(a))。円,楕円の描画に必要な6クロックのうち,1面に対する描画で4クロックかかる描画実行期間のみ3倍の12クロックになるからである。

表 4(b)に示した画面クリアは塗りつぶしの一例である。 内蔵レジスタに格納している塗りつぶしパターンをクリア 用のパターンとして参照しながら四辺形を塗りつぶす。四 辺形の左辺と右辺がビット境界の場合は、そのワードの塗 りつぶしにマスク処理が必要になり、リード・モディファ イ・ライトを実行する。しかし、この画面クリアではビット境界はない。11万5200ワードを28.8 msで実行する。これから、1ワードを2クロックでクリアできることがわかる。四辺形内塗りつぶし以外の塗りつぶしでは、塗りつぶし速度は塗りつぶしパターンの参照方法にほとんど依存していない。塗りつぶしパターンの参照方法により読み出し時間は異なるが、これよりも塗りつぶし領域を確定するた めの座標計算や境界点検索に要する時間が長いからである。

任意閉領域内塗りつぶしは非常に高速である(表4(b))。この例では図14(b)に示したように画面の約80%を塗りつぶしている。しかし、3面で構成する画面全体を他の3面へコピーする時間と比べて約2倍弱でしかない。コピーでは定められた単純な描画アドレス計算をすればよいが、ペイントでは境界点検索という複雑な処理をしている。この速度は、境界点検索を高速実行する前述したハードウエアと検索アルゴリズムの成果である。また、90度回転コピーと通常のコピーとの間で描画実行時間にはそれほど差異は生じてこない。通常のコピーの約2倍の時間で拡大、約3倍の時間で縮小ができると思ってよい。

24×24ドットの文字フォントを展開する描画時間は、大きな領域に対するコピーとは別個に評価した。ここではワード境界ではなくビット境界にフォントを描画している。 描画開始座標を直線発生器により算出している傾斜展開と通常展開で実行時間にほとんど差は出ていない。並列処理とパイプライン処理が効率良く行なわれている証拠である。この連続的なグラフィックス文字描画の評価結果から計算して、1秒間に白黒で1万3640字、8色で8040字の24×24ドット構成のグラフィックス文字描画ができることになる。この値は描画サイクル時のクロック数を基にして机上で算出したものと比べると、かなり低い数字になるが、より実際的な数字である。

### CGI準拠や高速化が可能

VDI あるいはその簡略版ともいえる CGI といったグラ フィックス・インタフェース規格のとりまとめ作業が進ん でいる。グラフィックス・コントローラが新しく開発され るたびに、これらの規格へどのように対応しているかが話 題になるようである。結論から言えば、CGI の定めたコマ ンドを直接解釈できるコントローラが出現するのはまだま だ先のことになる。規格が完全に固まり、グラフィックス 標準として一般に浸透し、実績のある枯れたソフトウエア になった段階で、ようやく LSI 化に向かうことになろう。

「CGI に準拠している」とするコントローラもあるが、こ れには議論の余地がある。CGI インタプリタは、コマンド 解釈部分とデバイス・ドライバ部分に大別できる。 コマン ド解釈部分はコントローラに依存しないため、異種のコン トローラであっても CPU が同じであれば流用できる。 CPU が異なっていても C 言語などで記述していれば問題 はない。使用するコントローラによって差が出てくるのは デバイス・ドライバ部分である。われわれは、このデバイ ス・ドライバがいかに簡単に作成できるかによって、「CGI に対する準拠度」が決まると考えている。

AGDC は、CGI の備える描画機能をほとんど内蔵してい る( $\mathbf{表}$  5)。したがって、 $\mathbf{AGDC}$  の必要とするパラメータを 生成するだけでよい。複雑な描画アドレス生成や表示メモ リを制御するソフトウエアの開発は要らない。内蔵してい ない描画機能を補完する場合だけ、ソフトウエア作成工数 を割り当てればすむ。

#### 3 次元表示やイメージ処理へ向けさらに高機能に

AGDC は GDC の開発によって築いた設計基盤にほとん ど依存しなかった。集積度が現在に比べると比較にならな いぐらい低かったころに設計した GDC は、ハード・ワイヤ ド・ロジックによって限定された描画機能を達成しなけれ ばならなかったからである。まったく新しいシステム構想 の下で, 描画アルゴリズム, 描画高速化のための専用ハー ドウエア, それらを効果的に制御するプリプロセサや描画

プロセサ,個々のハードウエアやソフトウエアなど,すべ てを設計基盤がない状態から徐々に積み上げながら開発し ていかなければならなかった。暗中模索の状態が長く続い た。AGDCはまったく新しい第2世代のグラフィックス・ コントローラとして開発したことになる。そのため、どの ようなコントローラが最適であるかについて、装置設計者 の側に立って隅々にまで細かい配慮をした。

最高動作周波数は8MHzであるが、今後チップ寸法を 縮小することによって高速化する予定である。ある機能が 達成されれば、次により高度な機能をもつ製品を開発する ことになるのは当然の流れである。3次元グラフィックス 機能への飛躍やイメージ処理への展開をすることになるだ ろう。さらに、デュアル・ポート・メモリが搭載する機能 を活用したり、機能を新たに搭載することにより、効果的 な機能分担をしていくことも考えられる。いずれにせよ, 次期開発製品からはこの AGDC を基盤として、機能を追加 していくことになる。今回経験したほどの障壁にはぶつか らないですむであろう。

#### 参考文献

- 1) 小口,「1ドットを 800 ns で描画できるラスタ走査型 CRT 用グラ フィック・コントローラ LSI」,『日経エレクトロニクス』, 1981 年 10月12日号, no. 275, pp. 186-209.

- 2) Pinkham, R., Novak, M. and Guttag, K., "Video RAM Excels at Fast Graphics," *Electronic Design*, Aug. 18, 1983, pp. 161-171.

- 3) 小林,「間断のないシリアル出力を可能にしたフレーム・バッファ 用 256 K ビット・デュアル・ポート・メモリを開発」,『日経エレ クトロニクス』, 1985 年 8 月 12 日号, no. 375, pp. 211-240.

- 4) Wientjes, B., Guttag, K. and Roskell, D., "First Graphics Processor Takes Complex Orders to Run Bit-mapped Displays," Electronic Design, Jan. 23, 1986, pp. 73-81.

- 5) 御法川, 上野, 吉田, 武田, 前島, 桂, 「座標で描画位置を指定で き、塗りつぶしやコピーなど豊富なコマンドを持つ CRT コント ローラ」,『日経エレクトロニクス』, 1984年5月21日号, no. 343, pp. 221-254.

- 6) 稲葉,「ワークステーションのマルチウインドウ表示方法を比較 する」,同上,1985年7月29日号,no.374,pp.141-161.

- 7) 小口, 南野, 樋口, 「グラフィックス・ディスプレイ・コントロー ラ」,『トランジスタ技術』, 1983年1月号, pp. 320-343.

次ページに表5,略語一覧を掲載。

Aではじまるコマンドは絶対位置指定、Rは相対位置指定を示す。コマンド名の最後につけた A は絶対アドレス指 表 5 AGDC のコマンド一覧 定,Cは座標指定,Dは描画プロセサの座標をもとにする描画,Mは座標を新しく設定し直す描画を意味している。

| コマンド名                                                          | 設定するパラメータおよび動作内容                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| READ_DP<br>READ_COL                                            | 描画プロセサの $X$ と $Y$ 座標をプリプロセサに転送<br>指定した座標の色情報をプリプロセサに転送                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DOT_D<br>A_DOT_M<br>R_DOT_M                                    | (X#, Y#)に1ドット描画<br>(X, Y) に1ドット描画<br>(X+DX, Y+DY) に1ドット描画                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| A_LINE_M<br>A_LINE_D<br>R_LINE_M<br>R_LINE_D<br>A_REC<br>R_REC | $(X, Y)$ - $(X_E, Y_E)$ 間の直線描画 $(X \#, Y \#)$ - $(X_E, Y_E)$ 間の直線描画 $(X, Y)$ - $(X + DX, Y + DY)$ 間の直線描画 $(X \#, Y \#)$ - $(X + DX, Y + DY)$ 間の直線描画 $(X, Y)$ - $(X_S, Y_S)$ で定義する四辺形描画 $(X, Y)$ - $(X + DX, Y + DY)$ で定義する四辺形描画                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CRL ARC CSEC CSEG ELPS EARC ESEC                               | 中心 ( <i>X</i> c, <i>Y</i> c), 半径 <i>DX</i> で定義する円描画<br>中心 ( <i>X</i> c, <i>Y</i> c), 半径 <i>DX</i> , 開始点 ( <i>X</i> s, <i>Y</i> s), 終了点 ( <i>X</i> E, <i>Y</i> E) で定義する円弧描画<br>中心 ( <i>X</i> c, <i>Y</i> c), 半径 <i>DX</i> , 開始点 ( <i>X</i> s, <i>Y</i> s), 終了点 ( <i>X</i> E, <i>Y</i> E) で定義する円弧扇形描画<br>中心 ( <i>X</i> c, <i>Y</i> c), 半径 <i>DX</i> , 開始点 ( <i>X</i> s, <i>Y</i> s), 終了点 ( <i>X</i> E, <i>Y</i> E) で定義する円弧弦形描画<br>中心 ( <i>X</i> c, <i>Y</i> c), <i>Y</i> 方向半径 <i>DY</i> , <i>X</i> と <i>Y</i> の方向半径 2 乗比 <i>DH</i> , <i>DV</i> で定義する楕円描画<br>中心 ( <i>X</i> c, <i>Y</i> c), <i>X</i> 方向半径 <i>DX</i> , <i>Y</i> 方向半径 <i>DY</i> , <i>X</i> と <i>Y</i> の方向半径 2 乗比 <i>DH</i> , <i>DV</i> および開始点 ( <i>X</i> s, <i>Y</i> s), 終了点<br>( <i>X</i> E, <i>Y</i> E) で定義する楕円弧描画<br>中心 ( <i>X</i> c, <i>Y</i> c), <i>X</i> 方向半径 <i>DX</i> , <i>Y</i> 方向半径 <i>DY</i> , <i>X</i> と <i>Y</i> の方向半径 2 乗比 <i>DH</i> , <i>DV</i> および開始点 ( <i>X</i> s, <i>Y</i> s), 終了点<br>( <i>X</i> E, <i>Y</i> E) で定義する楕円弧扇形描画<br>中心 ( <i>X</i> c, <i>Y</i> c), <i>X</i> 方向半径 <i>DX</i> , <i>Y</i> 方向半径 <i>DY</i> , <i>X</i> と <i>Y</i> の方向半径 2 乗比 <i>DH</i> , <i>DV</i> および開始点 ( <i>X</i> s, <i>Y</i> s), 終了点<br>( <i>X</i> E, <i>Y</i> E) で定義する楕円弧扇形描画 |

| PAINT                                                          | 境界点検索開始点 $(X, Y)$ , 境界色指定 $DX$ による任意閉領域内塗りつぶし境界点検索開始点 $(X, Y)$ の色以外を境界色とする任意閉領域内塗りつぶし                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| A_REC_FILL_A<br>A_REC_FILL_C<br>R_REC_FILL                     | 開始絶対アドレス EAD1, 水平方向ドット数 $DH$ , 垂直方向ドット数 $DV$ で定義する四辺形内塗りつぶし $(X,Y)$ - $(Xs,Ys)$ で定義する四辺形内塗りつぶし $(X,Y)$ - $(X+DX,Y+DY)$ で定義する四辺形内塗りつぶし                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CRL_FILL<br>ELPS_FILL                                          | 中心 $(Xc, Yc)$ , 半径 $DX$ で定義する円内塗りつぶし中心 $(Xc, Yc)$ , $Y$ 方向半径 $DY$ , $X$ と $Y$ の方向半径 $2$ 乗比 $DH$ , $DV$ で定義する楕円内塗りつぶし                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| A_TRI_FILL<br>A_TRA_FILL<br>R_TRA_FILL                         | (X, Y)- $(Xs, Ys)$ - $(Xc, Yc)$ で定義する三角形内塗りつぶし $(X, Y)$ - $(Xs, Y)$ - $(Ys, Ye)$ - $(Xe, Ye)$ で定義する台形内塗りつぶし 上辺左の点 $(X, Y)$ , 右の点 $(Xs, Y)$ , 上辺と下辺の相対変位 $DY$ , 第 $3$ 点の $X$ からの相対変位 $DX$ , 第 $4$ 点の $Xs$ からの相対変位 $Xc$ で定義される台形内塗りつぶし                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| A_COPY_AA<br>A_COPY_AC                                         | 転送源の転送開始ワードアドレス EAD2, ドットアドレス dAD2, 転送先の転送開始ワードアドレス EAD1, ドットアドレス dAD1, 水平方向ドット数 $DH$ , 垂直方向ドット数 $DV$ で定義する領域間の転送 転送源の転送開始ワードアドレス EAD2, ドットアドレス dAD2, 転送先の転送開始点 $(X,Y)$ , 水平方向ドット数 $DH$ , 垂直方向ドット数 $DV$ で定義する領域間の転送                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| A_COPY_CA                                                      | 転送源の転送開始点 $(X_s, Y_s)$ , 転送先の転送開始ワードアドレス $EAD1$ , ドットアドレス $DH$ , 本平方向ドット数 $DH$ , 垂直方向ドット数 $DV$ で定義する領域間の転送                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| A_COPY_CC                                                      | 転送源の転送開始点 $(X_s, Y_s)$ , 転送先の転送開始点 $(X, Y)$ , 水平方向ドット数 $DH$ , 垂直方向ドット数 $DV$ で定義する領域間の転送                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| R_COPY_CC                                                      | 転送源の転送開始点 $(X_s, Y_s)$ , 転送先の転送開始点 $(X_s + X_c, Y_s + Y_c)$ , 水平方向ドット数 $DH$ , 垂直方向ドット数 $DV$ で定義する領域間の転送                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PUT_A PUT_C GET_A                                              | 転送先の転送開始ワードアドレス EAD1, ドットアドレス dAD1, 水平方向ドット数 $DH$ , 垂直方向ドット数 $DV$ で定義する表示メモリ領域への主記憶からの転送 転送先の転送開始点 $(X,Y)$ , 水平方向ドット数 $DH$ , 垂直方向ドット数 $DV$ で定義する表示メモリ領域への主記憶からの転送 転送源の転送開始 $DV$ で定義する表示メモリ領域への主記憶からの転送 転送源の転送開始の一ドアドレス EAD1, ドットアドレス dAD1, 水平方向ドット数 $DV$ で定義する ままえまり 領域から 主記憶 の の転送                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| GET_C                                                          | 表示メモリ領域から主記憶への転送<br>転送源の転送開始点 $(X, Y)$ ,水平方向ドット数 $DH$ ,垂直方向ドット数 $DV$ で定義する表示メモリ領域から主記憶への転送                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

#### 略語一覧(ABC順)

AGDC: Advanced Graphics Display

Controller

bitblt: bit block transfer CAS: column address strobe CGI: computer graphics interface CPU: central processing unit FIFO: first-in first-out

GDC: Graphics Display Controller ISSCC: International Solid State Circuits Conference

JIS: Japan Industrial Standard

LSI: large scale integrated circuit

OA: office automation

RAM: random access memory RAS: row address strobe ROM: read only memory VDI: virtual device interface

Article: A Graphics Display Controller LSI (Successor of µPD7220) with Enhanced Copy and Paint Functions

NEC has developed a new graphics display controller LSI -- AGDC ( $\mu$ PD72120). Based on its predecessor GDC ( $\mu$ PD7220), which was placed on the market in 1982, the features of  $\mu$ PD72120 include an enhanced bit map processing function, a copy function of rectangular areas which include enlargement, shrinkage and rotation and a fill function of triangles and trapezoids. Within the LSI, a preprocessor for executing draw preprocessing is mounted in addition to a drawing processor. The CPU, preprocessor and drawing processor are arranged for 3-stage pipeline processing to enhance system performance. Capacity of the display memory can be increased to 32 M bytes (max.) using dual port memory chips.  $\mu$ PD72120 operates with clocks up to 8 MHz. (NIKKEI)

The article was translated from the Japanese in the "Nikkei Electronics / Feb. 23 , 1987".

### A Graphics Display Controller LSI (Successor of µPD7220) with Enhanced Copy and Paint Functions

| Internal Architecture with A Multiprocessor Configuration                                                 | 6  |

|-----------------------------------------------------------------------------------------------------------|----|

| Up to 32 M Bytes Display Memory Consisting of Dual Port Memory Chips Can Be Controlled                    | 12 |

| A Command Interface of Parameter Direct Transfer Method is Adopted                                        | 19 |

| Drawing Processor Used To Execute High-Speed Processings of Enlargement, Shrinkage, Rotation and Painting | 23 |

| Evaluation of Actual Execution Speeds by Means of Various Benchmark Tests                                 | 31 |

| Conformity to CGI and Upgrading to Higher Speeds are Considered                                           | 37 |

NEC announced the graphics draw/display μPD7220 (GDC) at the ISSCC in February of 1981. Since then, this LSI has been used in a wide area of applications, such as OA equipment, fishphotocomposers and satellite finder. terminals. The GDC can directly control a display memory of up to 512 K bytes which is separated from the system bus. This LSI is equipped with functions to draw straight lines, arcs, graphics characters, etc. in high speeds. (Ref. Although speeds of drawing dimensional objects such as straight lines and arcs are thus increased. the GDC not equipped with a two is dimensional draw function (i.e. that of areas), such as paint and character font expansion for the bit map memory. The CPU then needs to perform their supplementary functions.

The newly developed µPD72120 (AGDC) aims to minimize supplementation by the CPU. Rich draw functions are added to the graphics controller and the drawing speeds are increased. As far as graphic draw functions are concerned, differences between the GDC and AGDC are not remarkable except that an ellipse, an arc, a sector and a chord can now be drawn by using single commands.

During the design of the AGDC, it was attempted to mount as many bit map

processing functions (which were missing in the GDC) as possible: data transfer between display memories (copy or bitblt function). paint function arbitrary closed area and unconditional fill functions in a circle, an ellipse, a triangle and a trapezoid. (See Figure 1 (a).) Among these functions, the copy function plays an important role in expanding character fonts and displaying the window. Also, during a copy, a graphic can be slanted or rotated through an arbitrary angle and, under some restrictions, enlarged or shrinked by an arbitrary factor. (See Figure 1 (b).) Together with the enhanced bit map functions, a put function and a get function, which are used when dimensional data stored on the main storage are expanded in dimensional manner on the display memory or vice versa, are also added.

Although these functions can also be offered using a general processor, it is then not practical to expect sufficient (Ref. 4) drawing speeds. Typical drawing speeds of the AGDC, when it is operated at a clock frequency of 8 MHz are given below. While drawing a straight line. the AGDC takes 500 ns to draw a bit or 1 pixel. If a copy function is used, 13,640 characters of 24 x 24 dot character font can be expanded in one second.

Rapid Shift From Character Display To Graphics Display:

As the memory price has lowered these years, there have been rapid changes in the display technology, that is, from character display to graphics display. Even for word processors, it now seems that handling of graphics data is a minimum condition. But graphics display requires a large memory capacity and its control is not easy. To change a character on a character display screen, for example, it is only necessary to rewrite one byte or one word of the character code memory contents. On a graphics display screen, however, it necessary to expand the becomes character font on the display memory again. If this is processed by the CPU, the rewriting speed is too slow. painting a complex figure is too great a burden for the CPU.

For this reason, there have been attempts to implement high-speed bit map functions using special gate circuits. But, due to restraints on the integration level and speed of gate arrays, it has not been possible to execute macro drawing functions like the filling of a triangle. So, at each of these small steps, the CPU needed to participate in the drawing. If the drawing speed is evaluated in small-step units. the speed of the array circuit is high. But from the viewpoint of an overall system, its performance often fails to meet expectations.

From this background, since the GDC appeared, many graphics controller LSI's with enhanced drawing functions have been announced. Table 1 lists some typical controller LSI's. These products show different features depending on design objectives of the manufacturers. Am95C60 (of Advanced Micro Devices, Inc., U.S.A.) and AGDC aim to implement high-speed drawing functions by means of hardware, while HD63484 (of Hitachi) tries to emphasize its display control function. 82786 (of

Intel, U.S.A.) mainly tries to enrich its display control function and TMS34010 (of Texas Instruments Inc, U.S.A.) is equipped with a built-in processor so that drawing software can be created freely.

Another important move to be noted concerning graphics display is the appearance of dual port memory chips with a line buffer. The first product was a 64 K dynamic RAM chip having a serial memory type built-in line buffer. (Ref. 2) After this, 256 K dual port memories with a random access type line buffer which are equipped with real-time data transfer function, pointer control function and write per bit function were announced.

The use of dual port memory chips markedly increases possible draw timings, to make the best use of the potential power of a continuous drawing controller.

#### Improve a System Performance

The AGDC is equipped with dual port memories. The AGDC has been designed to improve the system performance through the combined graphics control LSI and the CPU. Its internal architecture adopts a multi-processor configuration. Separate from the drawing processor, a processor especially for pre-drawn processings (called a preprocessor) is included.

preprocessor performs The processings such as address conversion from X-Y coordinates to absolute addresses. As the command interface, CPU directly writes parameters into the built-in register of the preprocessor. The preprocessor operates independently of the drawing processor and, as a result, the CPU can execute its pre-drawn processings such as command interpretation of CGI and BASIC and driving of the AGDC; the preprocessor can perform its pre-drawn

processings and the drawing processor can draw in a 3-stage pipeline manner when viewed as a system.

In addition, during the research of the drawing algorithm, a special hardware suiting the algorithm was designed to improve the drawing speed. The drawing tightly processor was designed to control these hardware components and, even when drawing types change, adapt to the various applications. Note that, in each step to be executed in a clock cycle of 125 ns (at 8MHz), up to 6 commands and direct branches can be executed. The execution of each command can use a command prefetch function as pipelining and, so, the operation of the processor itself includes both modes of pipeline parallel processing and processing.

#### Non-Compatible with GDC:

We greatly improved the functions rather than maintain compatibility with the GDC