# **NEC Microcomputers, Inc.**

#### PROGRAMMABLE CRT CONTROLLER

#### DESCRIPTION

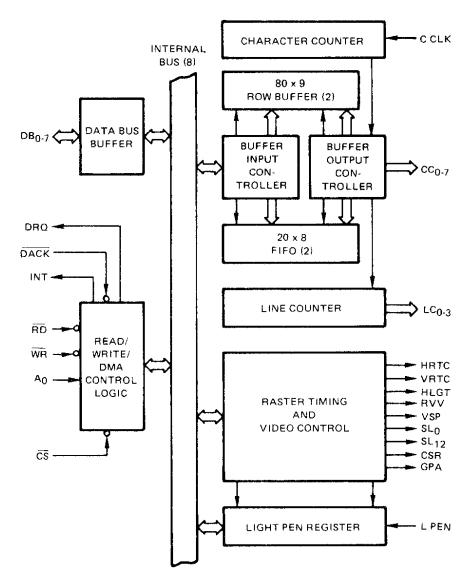

The  $\mu$ PD3301 is an LSI chip designed for use in CRT controllers. It contains a synchronous signal generator, row buffer, and attribute memory. This CRT controller is capable of handling not only black and white CRT, but also color CRT. The  $\mu$ PD3301 provides control signals which simplify the design of the external circuitry needed in the systems. Thus, this device is a versatile controller that relieves the main CPU (and users) of many of the control burdens associated with implementing a CRT interface.

There are 8 separate commands which the  $\mu$ PD3301 will execute. Some of these commands require multiple bytes to fully specify the operation which the processor wishes the CRT controller to perform. The following commands are available:

- RESET

- STOP DISPLAY

- START DISPLAY

- SET INTERRUPT MASK

- READ LIGHT PEN

- LOAD CURSOR POSITION

- RESET INTERRUPT

- RESET COUNTERS

#### FEATURES

- Programmable Screen and Character Format Capabilities;

- Characters per Row (up to 80 characters/row)

- Lines per Character (up to 32 lines/character)

- Rows per Frame (up to 64 rows/frame)

- Horizontal Retrace Time

- Vertical Retrace Time

- Blinking Time

- DMA Control Mode

- Cursor Control Mode

- Three Independent Visual Field Attribute Modes such as;

- Transparent Attribute Color Mode

- Transparent Attribute Black and White Mode

- Non-Transparent Attribute Black and White Mode

- 12 Independent Field Attribute Functions such as;

Vertical Line

Over-Line

Blue

Blinking

General Purpose

- Reverse Video - Under-Line - Green

- Secret - High-Light - General Purpose Color

- Light Pen Detection

- Maximum 256 Different Characters Control Capability

- Fully Bus Compatible with 8080

- 3 MHz Single Clock Input

- Single Power Supply, +5V N-MOS Technology

- Available in 40 pin Plastic and Ceramic Dual-In-Line Packages

#### PIN CONFIGURATION

#### VRTC [ 40 VCC (+5V) 39 D SLO RVV [ 38 LC0 CSR [ 3 L PEN 37 LC<sub>1</sub> INT 🗖 5 36 LC2 DRQ 🗖 35 🗖 LC3 34 🗖 VSP DACK **1** 7 33 | SL<sub>12</sub> 32 | GPA 31 | HLGT 30 | CC<sub>7</sub> 29 | CC<sub>6</sub> A<sub>0</sub> | 8 RD | 9 WR | 10 μPD 3301 CS | 11 DB<sub>0</sub> | 12 DB<sub>1</sub> | 13 28 🗖 CC5 DB<sub>2</sub> 🗖 14 27 CC4 DB<sub>3</sub> 🗖 15 26 CC<sub>3</sub> DB4 🗖 16 25 CC<sub>2</sub> 24 🗖 CC1 DB<sub>5</sub> 🗖 17 DB<sub>6</sub> 🗖 18 23 CC<sub>0</sub> 22 🗖 C CLK DB7 🗖 19 GND [ 21 HRTC

### PIN NAMES

| VRTC              | Vertical Retrace          |

|-------------------|---------------------------|

| RVV               | Reverse Video             |

| CSR               | Cursor                    |

| L PEN             | Light Pen                 |

| INT               | Interrupt                 |

| DRQ               | DMA Request               |

| DACK              | DMA Acknowledge           |

| A <sub>0</sub>    | Address Bus 0             |

| RD                | Read                      |

| WR                | Write                     |

| ĈŜ                | Chip Select               |

| DB <sub>0-7</sub> | Data Bus 0 to 7           |

| HRTC              | Horizontal Retrace        |

| C CLK             | Character Clock           |

| CC <sub>0-7</sub> | Character Codes 0 to 7    |

| HLGT              | High-light                |

| GPA               | General Purpose Attribute |

| SL <sub>12</sub>  | Slit Line 12              |

| VSP               | Video Suppression         |

| LC <sub>0-3</sub> | Line Counter 0 to 3       |

| SL <sub>0</sub>   | Slit Line 0               |

| ·                 |                           |

#### **Character Counter**

Counts the characters in a row, up to the number of the characters defined in Characters/Row.

#### **Row Buffer**

Consists of a dual RAM buffer. Each buffer can store up to 80 characters. During a DMA operation, the characters are written into the Row Buffer. One of the buffers is used for display. Each character in the buffer is read with Character Clock (C CLK), and the data appears in CC<sub>0-7</sub>. At the same time, the data on the next row is written into another buffer by DMA control.

#### **Buffer Input/Output Controller**

- Writes the characters into the Row Buffer, up to the number defined by Characters/Row.

- Outputs the data from the Row Buffer to CC<sub>0-7</sub>.

- Writes the attributes and special control character codes into the FIFO, up to the number defined by Attributes/Row.

- Reads the attribute codes from the FIFO and transfers them to the video circuit.

- In case of Non-Transparent Attribute Mode, it distinguishes an ordinary character code from an attribute code among the character data read from the Row Buffer.

#### FIFO (First Input, First Output)

Consists of a dual RAM buffer. Each buffer can store up to 20 characters. By DMA operation, attribute codes and special control characters are written into the FIFO. One of the buffers is used for display. Whenever the read flag bit for FIFO is detected, an attribute code is read and transferred to the video circuit. And at the same time, the attribute codes in the next row are written into the rest of the buffers (another buffer) by DMA operation.

#### **Line Counter**

Counts the events of Rasters/Line, up to the number indicated by Lines/Character.

#### Raster Timing and Video Control

- Outputs the HRTC based on the Character Counter during the time indicated by Horizontal Retrace Time.

- Outputs the VRTC based on Row Counter which counts up the contents, row by row, during the time indicated by Vertical Retrace Time.

- Outputs HLGT, RVV, VSP, SL<sub>0</sub>, SL<sub>12</sub>, GPA based on attribute codes transferred from the Buffer Output Controller.

- Outputs the CSR based on the Blinking Time etc. at the position indicated by Cursor Address.

#### Light Pen Register

Memorizes a row address and column address when the L PEN signal is input. By using READ LIGHT PEN instruction, the CPU can read the contents.

| Operating Temperature          |

|--------------------------------|

| Storage Temperature            |

| All Output Voltages            |

| All Input Voltages             |

| Supply Voltage V <sub>CC</sub> |

COMMENT: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

$$*T_a = 25^{\circ}C$$

$T_a = 0^{\circ} C \text{ to } +70^{\circ} C; V_{CC} = +5 V \pm 5\%$

| PARAMETER                 | SYMBOL | LIMITS |     |                       |      | TEST                                                                 |

|---------------------------|--------|--------|-----|-----------------------|------|----------------------------------------------------------------------|

|                           |        | MIN    | TYP | MAX                   | UNIT | CONDITIONS                                                           |

| Input Low Voltage         | VIL    | -0.5   |     | 0.8                   | V    |                                                                      |

| Input High Voltage        | VIH    | 2.2    |     | V <sub>CC</sub> + 0.5 | V    |                                                                      |

| Output Low Voltage        | VOL    |        |     | 0.45                  | V    | I <sub>OL</sub> = 1.6 mA                                             |

| Output High Voltage       | ∨он    | 2.4    |     | Vcc                   | ٧    | DB <sub>0-7</sub> : † <sub>OH</sub> = -150 μA,<br>All Others: -80 μA |

| Low Level Input Leakage   | 116    | _      |     | -10                   | μΑ   | V <sub>IN</sub> = 0V                                                 |

| High Level Input Leakage  | ЧН     |        |     | +10                   | μА   | V <sub>IN</sub> = V <sub>CC</sub>                                    |

| Low Level Output Leakage  | loL    |        |     | -10                   | μΑ   | V <sub>OUT</sub> = 0V                                                |

| High Level Output Leakage | ЮН     |        | l   | +10                   | μА   | V <sub>OUT</sub> = V <sub>CC</sub>                                   |

| Power Supply Current      | 1cc    |        | 90  |                       | mA   |                                                                      |

$T_a = 25$ °C;  $V_{CC} = 0V$

| DARAMETER          | 07/4001 | LIN | MITS | 1 15117 | TEST CONDITIONS                    |  |

|--------------------|---------|-----|------|---------|------------------------------------|--|

| PARAMETER          | SYMBOL  | MIN | MAX  | UNIT    | TEST CONDITIONS                    |  |

| Input Capacitance  | CIN     |     | 10   | pF      | fc = 1 MHz,<br>All Pins Except Pin |  |

| Output Capacitance | COUT    |     | 20   | pF      | Under Test Tied to<br>AC Ground    |  |

| PARAMETER                                     |                        | 0)/1406:         | LIM                    | IITS                   |      | TEST<br>CONDITIONS                              |

|-----------------------------------------------|------------------------|------------------|------------------------|------------------------|------|-------------------------------------------------|

|                                               |                        | SYMBOL           | MIN                    | MAX                    | UNIT |                                                 |

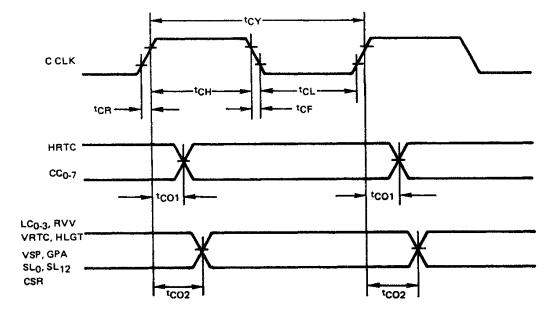

| Clock Cycle                                   | μPD3301-1              | <sup>t</sup> CY  | 0.5                    | 10                     | μs   |                                                 |

| Time                                          | μPD3301-2              | tCY              | 0.38                   | 10                     | μς   |                                                 |

| Clock High L                                  | _evel                  | <sup>t</sup> CH  | 150                    |                        | ns   |                                                 |

| Clock Low L                                   | .evel                  | <sup>t</sup> CL  | 150                    | 1000                   | ns   |                                                 |

| Clock Rise T                                  | ime                    | <sup>t</sup> CR  | 5                      | 30                     | ns   |                                                 |

| Clock Fall T                                  | ime                    | <sup>t</sup> CL  | 5                      | 30                     | ns   |                                                 |

| Output Dela                                   | y from C CLK ↑         | <sup>t</sup> CO1 | 0                      | 150                    | ns   | 1TTL + 15 pF:<br>HRTC, CC <sub>0-7</sub>        |

| Output Dela                                   | ·                      | tCO2             |                        | 400                    | ns   | 1TTL + 15 pF:<br>Except HRTC, CC <sub>0-7</sub> |

| from C CLK ↑                                  | <sup>†</sup> μPD3301-2 | <sup>†</sup> CO2 |                        | 300                    | ns   | LX00pt 111110, 000/                             |

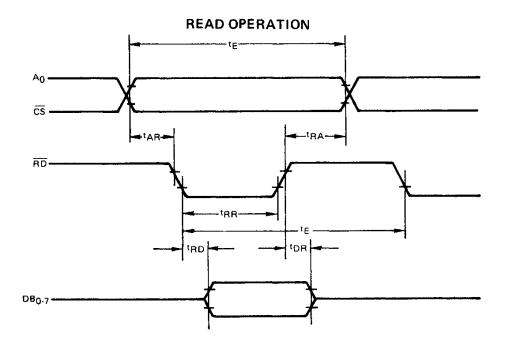

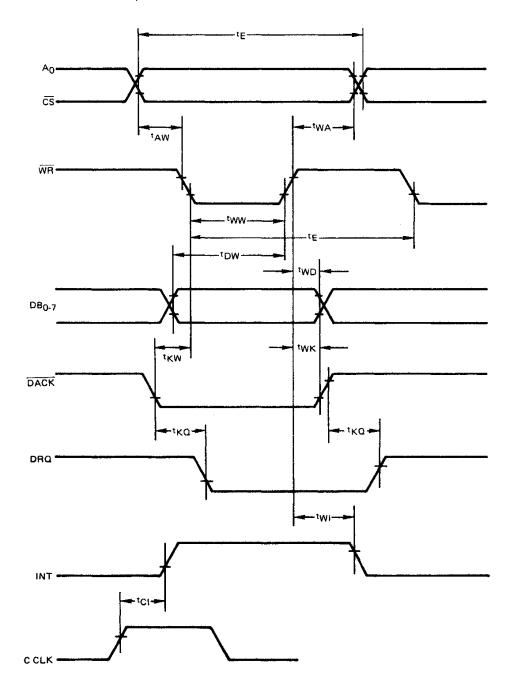

| Command C                                     | vole Time              | <sup>†</sup> E   | 2t <sub>CY</sub> + 200 |                        | ns   | t <sub>CY</sub> ≥ 400 µs                        |

| Communa                                       | y cie i iiiie          | t <sub>E</sub>   | 1                      |                        | μs   | t <sub>C</sub> γ < 400 μs                       |

| A <sub>0</sub> , $\overline{\text{CS}}$ Set U | Jp Time to WR          | tAW              | 0                      |                        | ns   |                                                 |

| A <sub>0</sub> , CS Hold                      | Time to WR             | tWA              | 0                      |                        | ns   |                                                 |

| WR Pulse Wi                                   | dth                    | tww              | 200                    |                        | ns   |                                                 |

| Data Set Up                                   | Time to WR             | tDW              | 150                    |                        | ns   |                                                 |

| Data Hold T                                   | ime to WR              | tWD              | 30                     |                        | ns   |                                                 |

| DACK ↓ Set                                    | Up Time to WR          | <sup>t</sup> KW  | 0                      |                        | ns   |                                                 |

| DACK 1 Hol                                    | d Time to WR           | tWK              | 0                      |                        | ns   |                                                 |

| DRQ Delay                                     | from DACK ↓            | tκα              | 0                      | 250                    | ns   | 1TTL + 50 pF                                    |

| INT Delay fr                                  | om WR ↑                | tWI              | t <sub>CY</sub> + 20   | 2t <sub>CY</sub> + 300 | ns   | 1TTL + 50 pF                                    |

| INT Delay from C CLK 1                        |                        | <sup>†</sup> CI  |                        | 300                    | ns   | 1TTL + 50 pf                                    |

| A <sub>0</sub> , CS Set Up Time to RD         |                        | t <sub>AR</sub>  | 0                      |                        | ns   |                                                 |

| A <sub>0</sub> , CS Hold Time to RD           |                        | <sup>t</sup> RA  | 0                      |                        | ns   |                                                 |

| RD Pulse Width                                |                        | <sup>t</sup> RR  | 300                    |                        | ns   |                                                 |

| Data Access Time from RD ↓                    |                        | <sup>t</sup> RD  | 0                      | 250                    | ns   | C <sub>L</sub> = 100 pF                         |

| Data Float Delay from RD ↑                    |                        | tDR              |                        | 150                    | ns   | C <sub>L</sub> = 100 pF                         |

|                                               |                        |                  | 20                     |                        | ns   | C <sub>L</sub> = 15 pF                          |

### **CLOCK AND OUTPUT DELAY**

DMA, INTERRUPT AND WRITE OPERATION

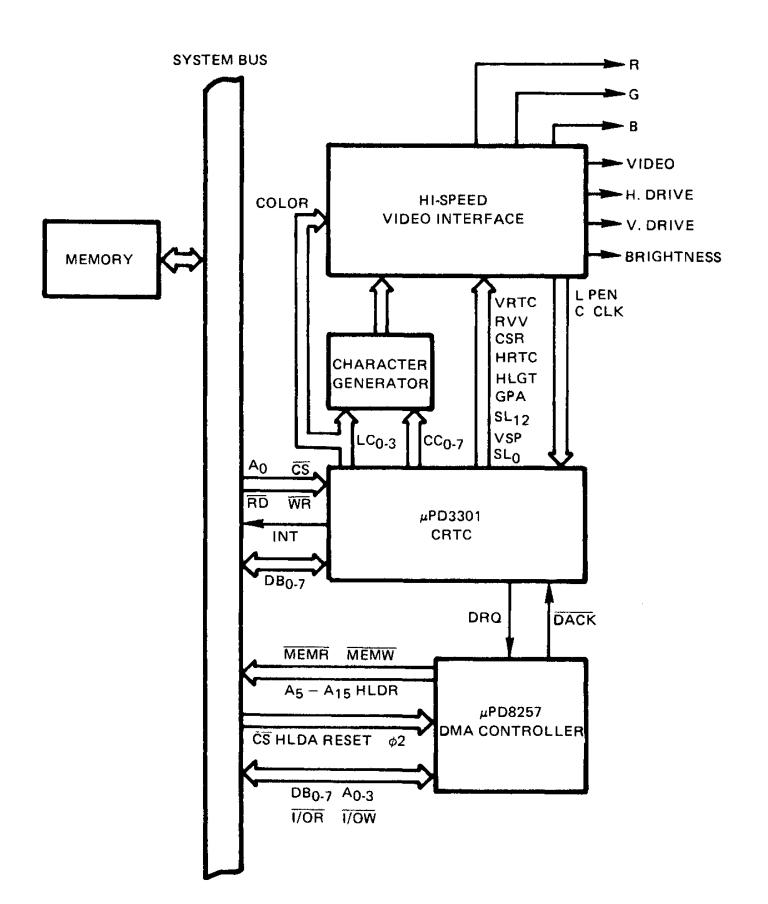

The data is transferred from the external memory which contains the information about characters and attributes to the Row Buffer under the control of  $\mu PD8257$  DMA Controller. The data read from the Row Buffer are Video Control Outputs and ROM Address Signal Outputs toward External Character Generator. The  $\mu PD3301$  also outputs horizontal and vertical retrace signals.

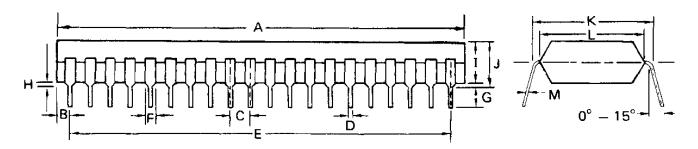

## (PLASTIC)

| ITEM | MILLIMETERS | INCHES        |

|------|-------------|---------------|

| A    | 51.5 MAX.   | 2.028 MAX.    |

| В    | 1,62 MAX.   | 0.064 MAX.    |

| С    | 2.54 ± 0.1  | 0.10 ± 0.004  |

| D    | 0.5 ± 0.1   | 0.019 ± 0.004 |

| E    | 48.26 ± 0.1 | 1.9 ± 0.004   |

| F    | 1.2 MIN.    | 0.047 MIN.    |

| G    | 2,54 MIN.   | 0.10 MIN.     |

| Н    | 0.5 MIN.    | 0.019 MIN.    |

| I    | 5.22 MAX.   | 0.206 MAX.    |

| J    | 5.72 MAX.   | 0.225 MAX.    |

| K    | 15.24 TYP.  | 0.600 TYP.    |

| L    | 13.2 TYP.   | 0.520 TYP.    |

| М    | 0.25 +0.1   | 0.010 +0.004  |

μPD3301C

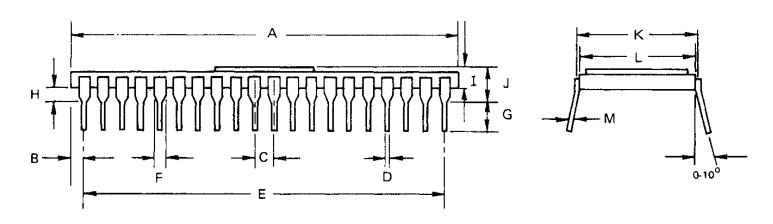

## (CERAMIC)

| ITEM | MILLIMETERS | INCHES        |

|------|-------------|---------------|

| Α    | 51,5 MAX.   | 2.03 MAX.     |

| В    | 1.62 MAX.   | 0.06 MAX.     |

| С    | 2.54 ± 0.1  | 0.1 ± 0.004   |

| D    | 0.5 ± 0.1   | 0.02 ± 0.004  |

| E    | 48.26 ± 0.1 | 1.9 ± 0.004   |

| F    | 1.02 MIN.   | 0.04 MIN.     |

| G    | 3,2 MIN.    | 0.13 MIN.     |

| Н    | 1.0 MIN.    | 0.04 MIN.     |

| I    | 3.5 MAX.    | 0.14 MAX.     |

| J    | 4,5 MAX.    | 0.18 MAX.     |

| Κ    | 15.24 TYP.  | 0.6 TYP.      |

| L    | 14.93 TYP.  | 0.59 TYP.     |

| М    | 0.25 ± 0.05 | 0.01 ± 0.0019 |

$\mu$ PD3301D