# 82C455 Flat Panel/CRT VGA Controller

- 100% IBM VGA-compatible

- Supports analog/digital CRT monitors and LCD, Plasma, and Electro Luminescent panels of varying resolutions

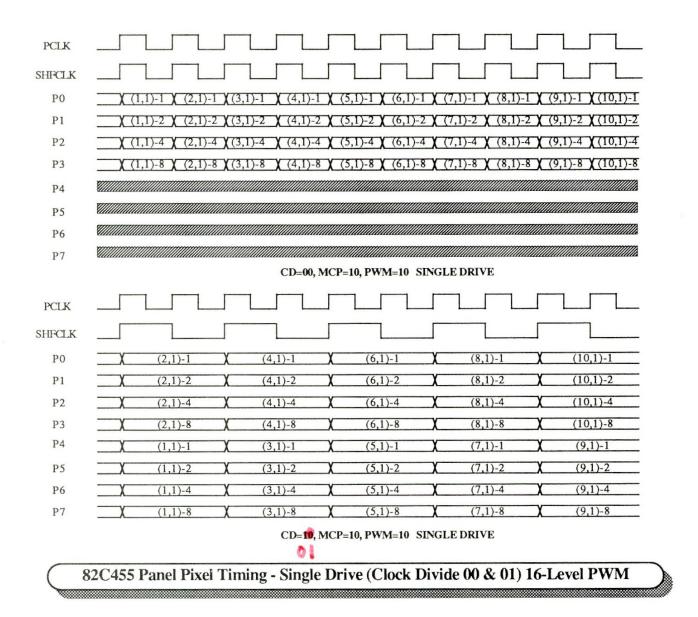

- Up to 16 gray levels on monochrome panels

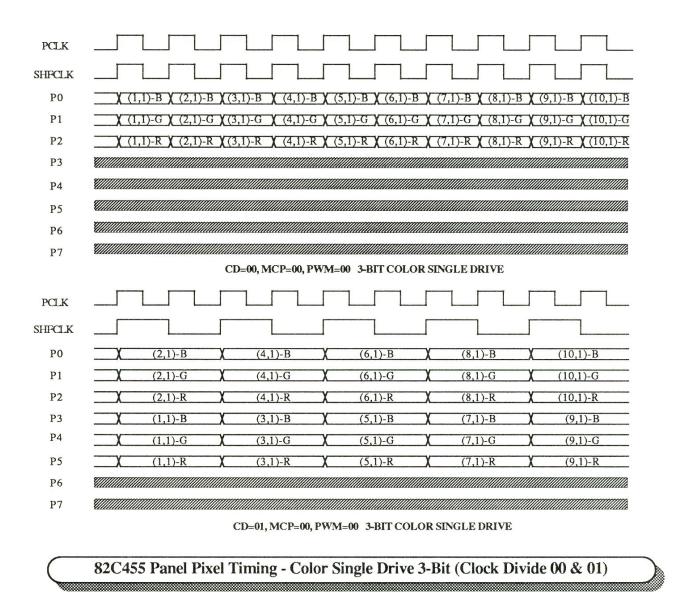

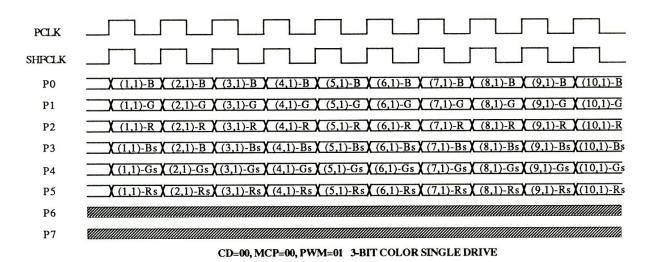

- Integrates full support of color panels

- Programmable vertical compensation techniques increase usable display area

- SMARTMAP<sup>TM</sup> intelligent color to gray level conversion

- Advanced SLEEP modes minimize power consumption

- Single chip implementation tightly couples to the CHIPS/280 and interfaces with 8- and 16-bit PC bus and MCA (an interface compatible with MicroChannel<sup>TM</sup>)

- Can utilize an external palette DAC with up to 16 million colors

- Full backwards compatibility with IBM EGA, CGA, MDA and Hercules graphics standards

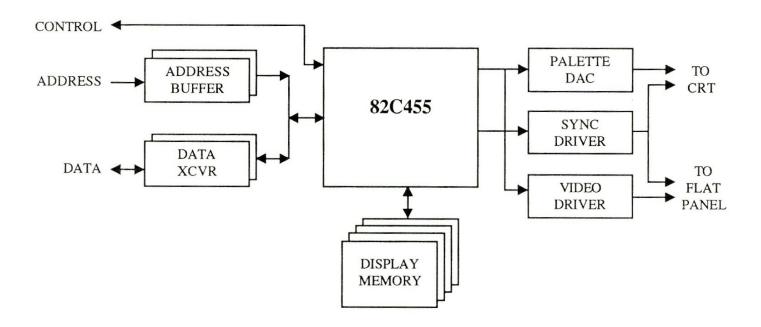

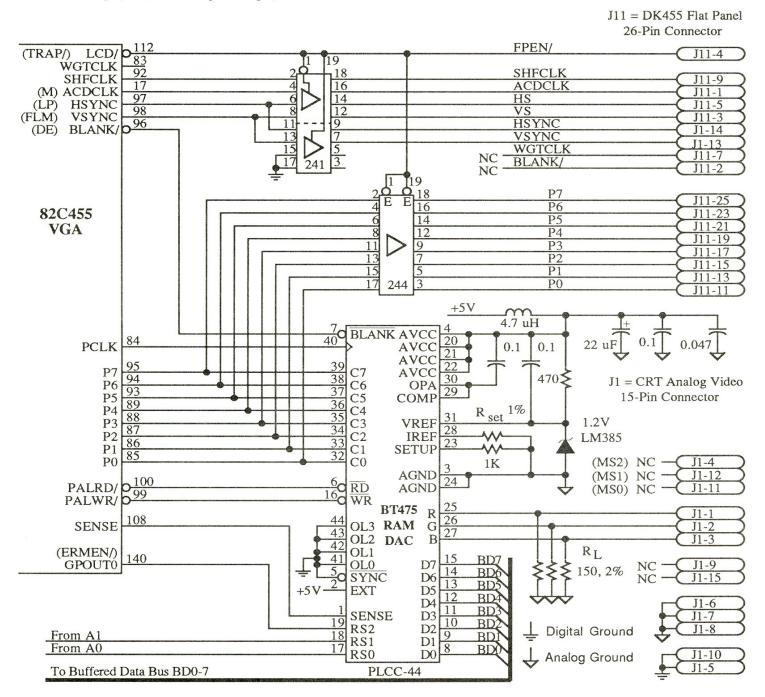

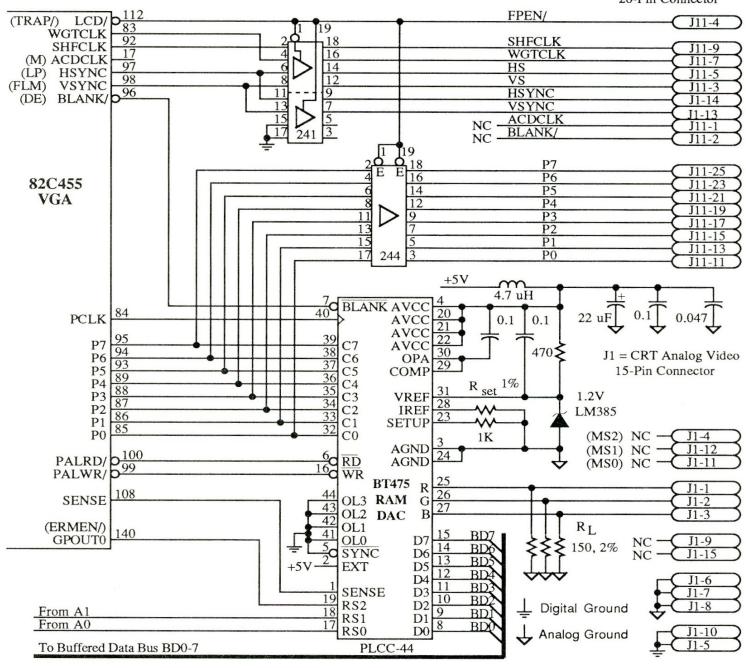

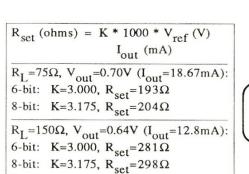

82C455 System Implementation

# Introduction

The 82C455 VGA Flat Panel/CRT controller provides a single-chip solution for a VGA, EGA, CGA, MDA, or Hercules compatible display system. The 82C455 supports a wide variety of flat panel displays and CRT monitors.

By providing a high level of integration, the 82C455 minimizes the total chip count for VGA display subsystems. The 82C455's power-down features reduce power consumption of the display subsystem and extend battery life in portable applications. The 82C455 provides a variety of programmable features, such as Vertical Compensation, SMARTMAP<sup>TM</sup> and Alternate Registers to enhance the flat panel display.

#### FLAT PANEL DISPLAYS

There is currently no standard interface for flat panel displays. Interface signals and timing requirements vary between panel technologies and manufacturers. The 82C455 provides register programmable features to allow interfacing to the widest possible range of flat panel display units.

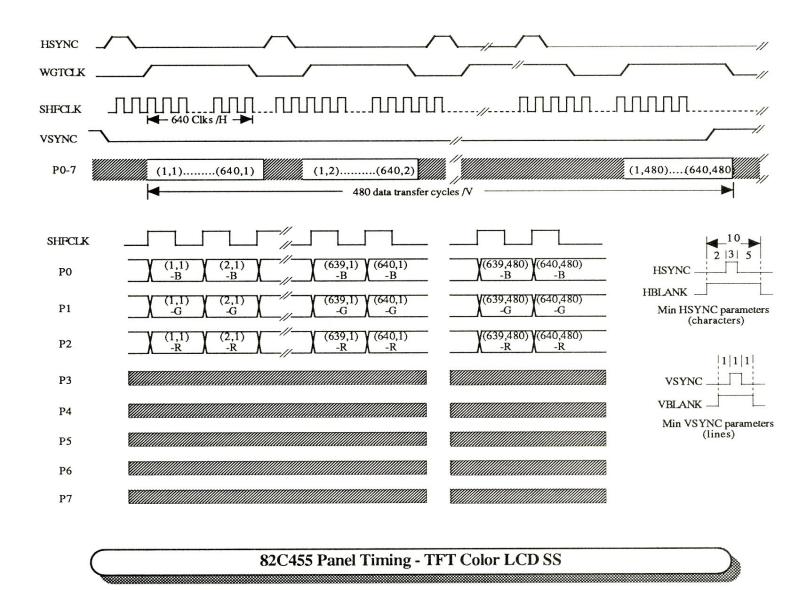

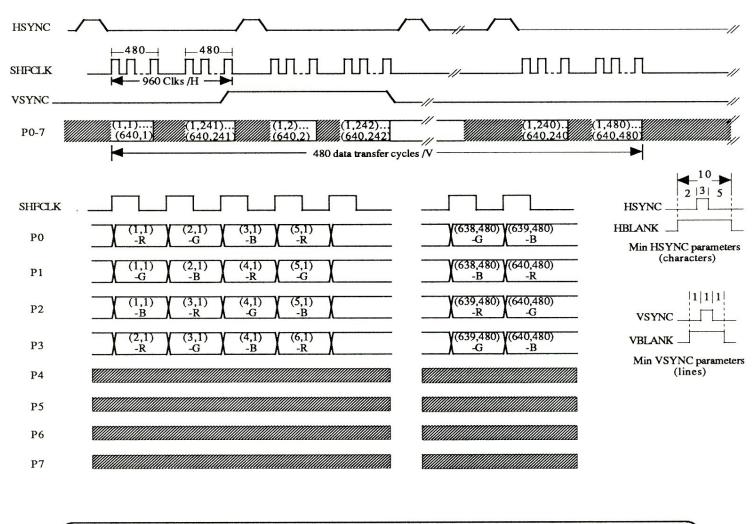

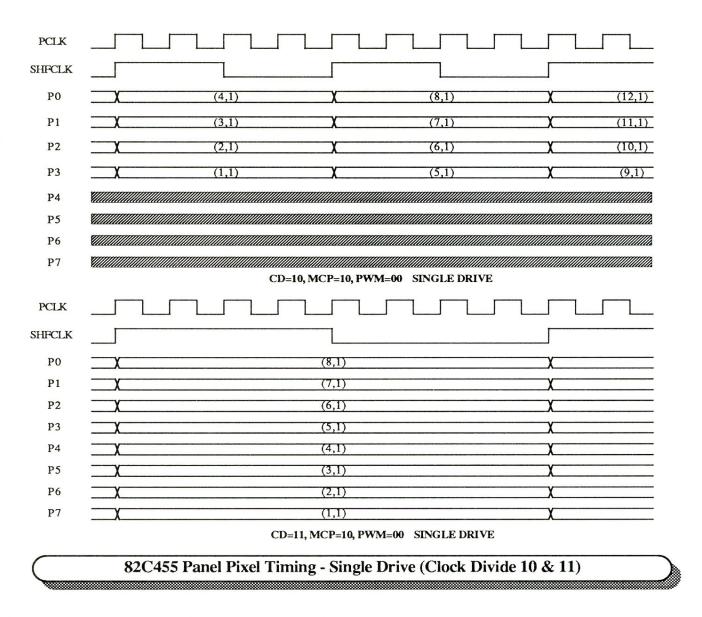

The 82C455 interfaces directly to monochrome, grayscale or color panels. A proprietary Frame Rate Control algorithm generates 16 gray levels on monochrome panels. (Frame Rate Control generates gray levels on monochrome panels by turning the pixels on and off over several frames.) The 82C455 outputs 16 level grayscale for panels which internally generate gray levels and drives color panels with up to 64 colors.

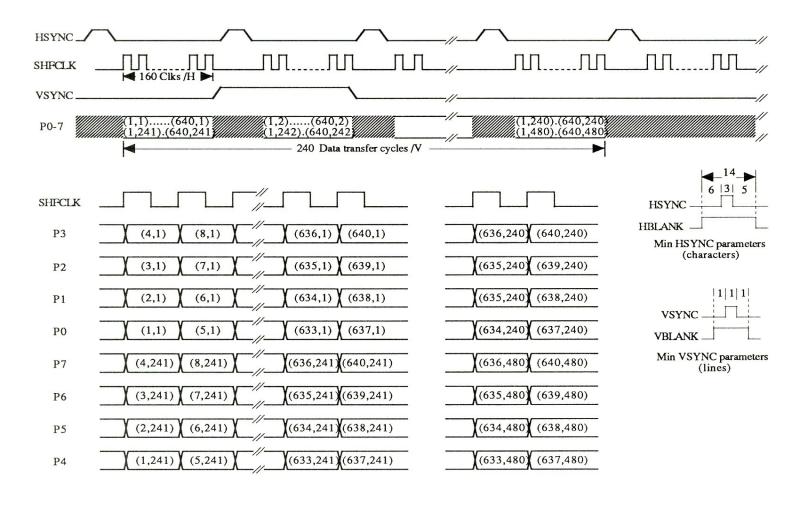

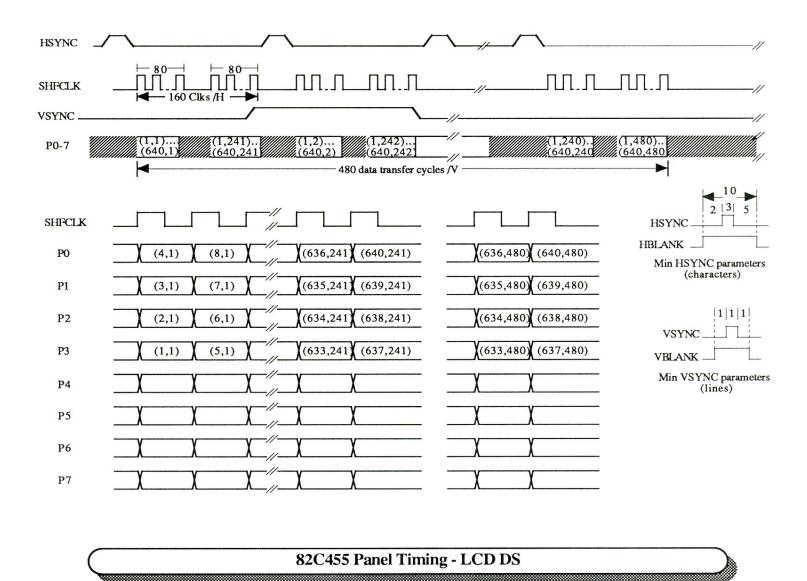

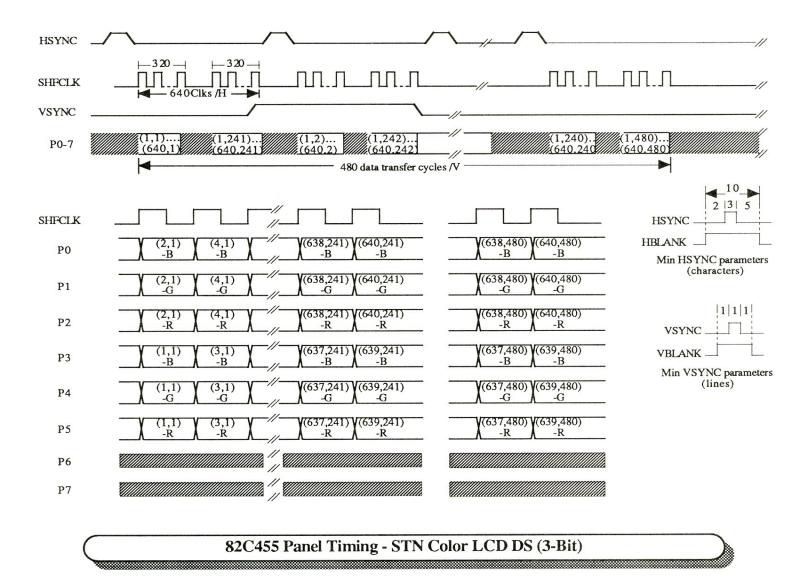

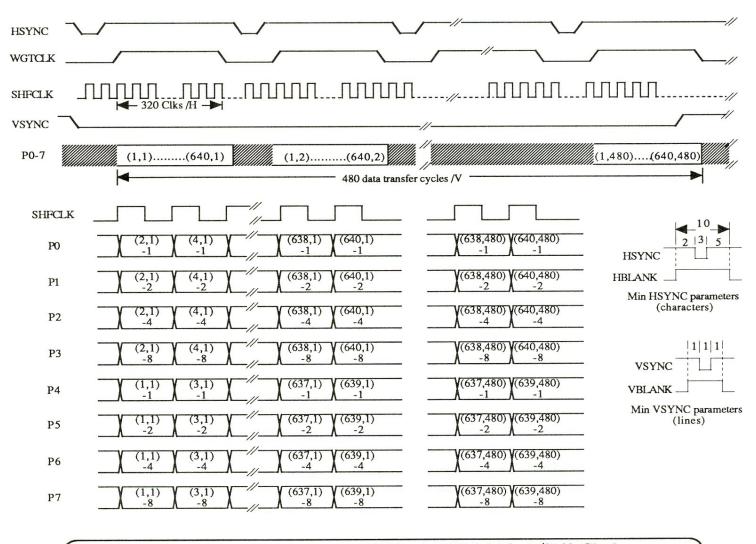

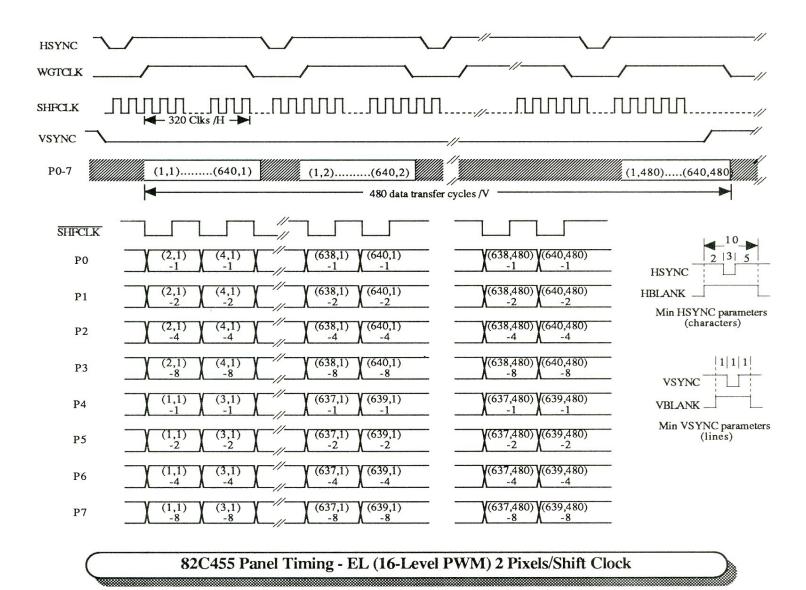

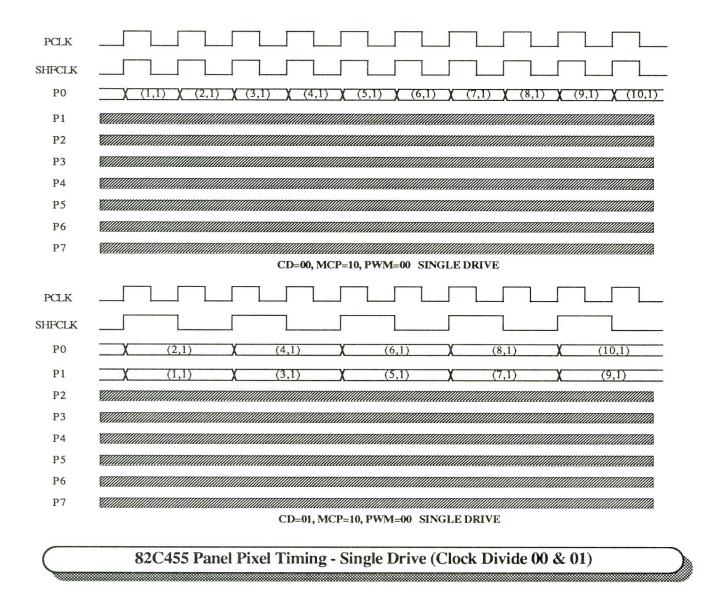

The 82C455 supports all flat panel display technologies including plasma, electroluminescent (EL) and liquid crystal displays (LCD). LCD panel interfaces are provided for single panel-single drive (SS), dual panel-single drive (DS), and dual panel dual drive (DD) configurations. A single panel sequences data similar to a CRT. In contrast, a dual panel requires video data sequence from separate locations in memory. In addition, a dual drive panel requires the sequence to occur simultaneously. The 82C455 handles the display data sequencing transparent to the application software providing full compatibility on both CRT and flat panel displays.

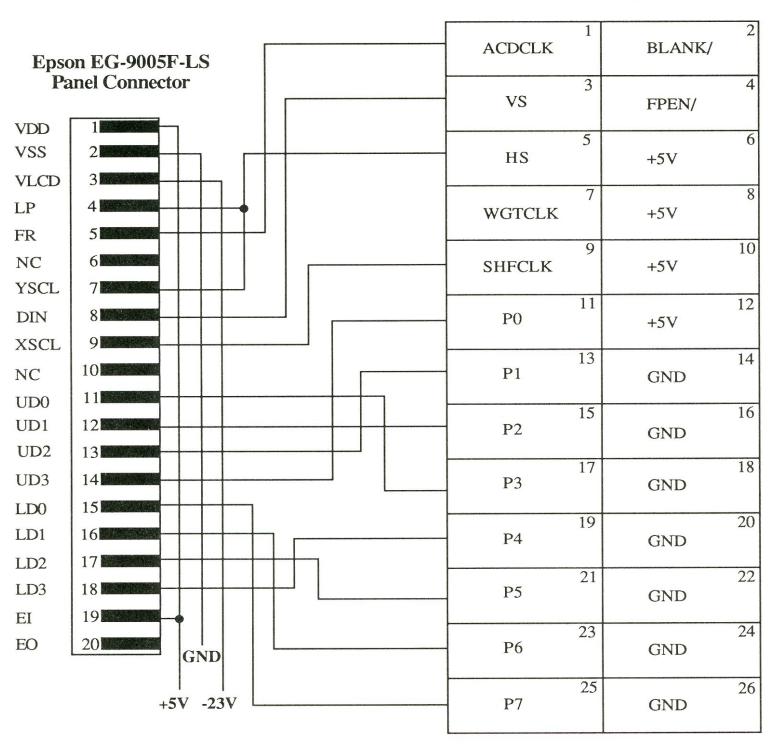

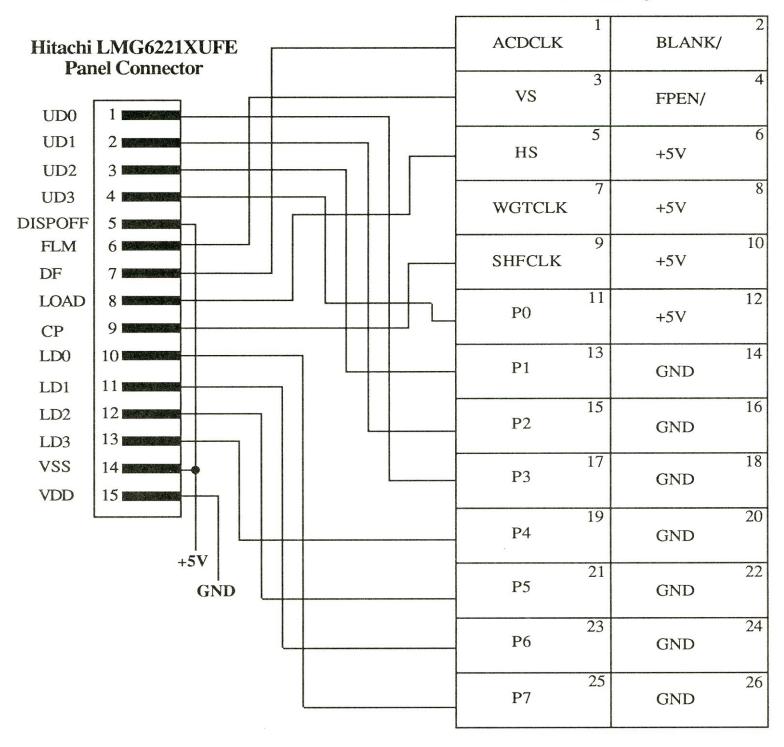

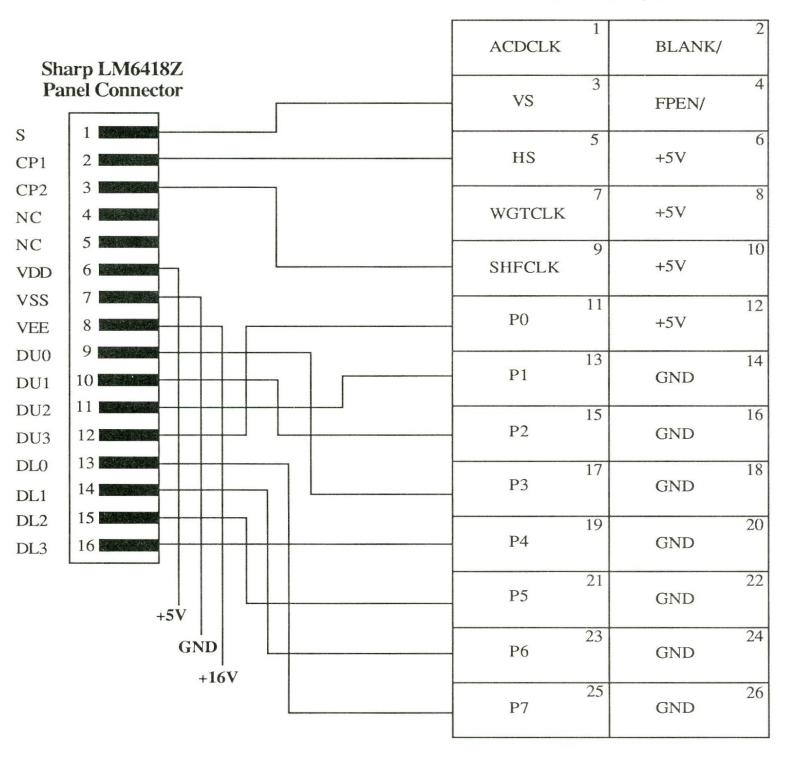

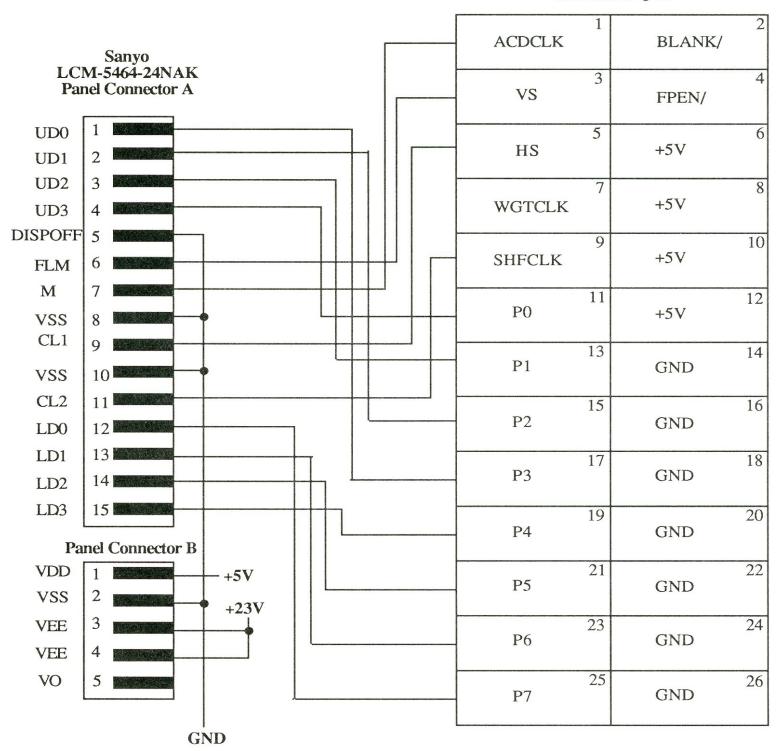

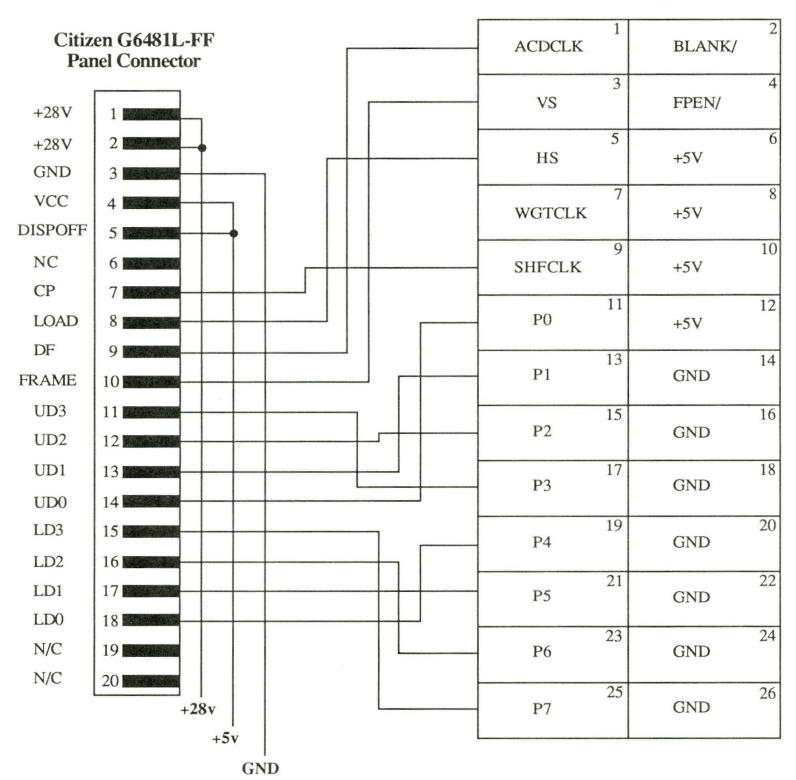

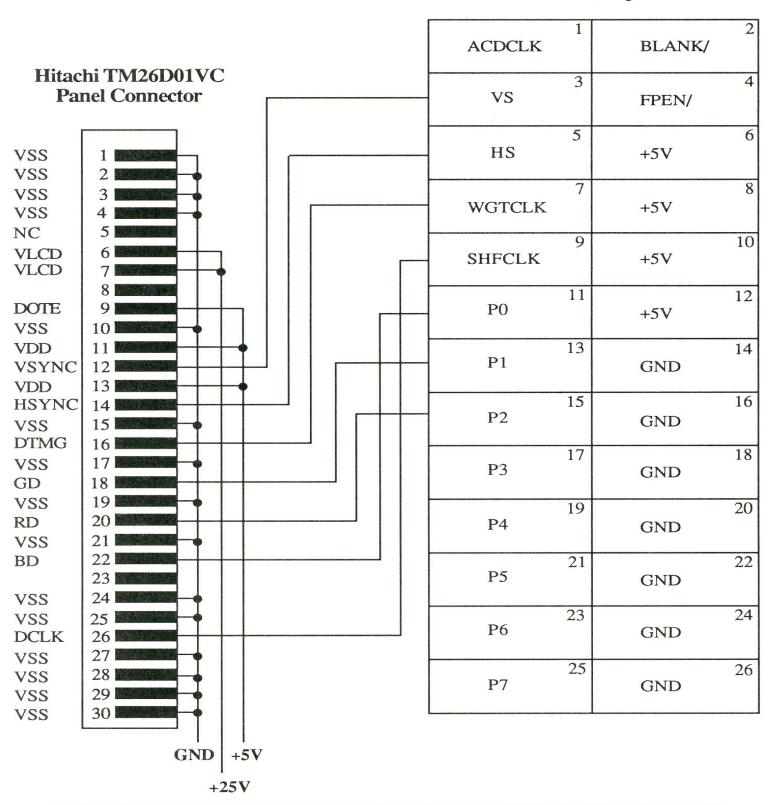

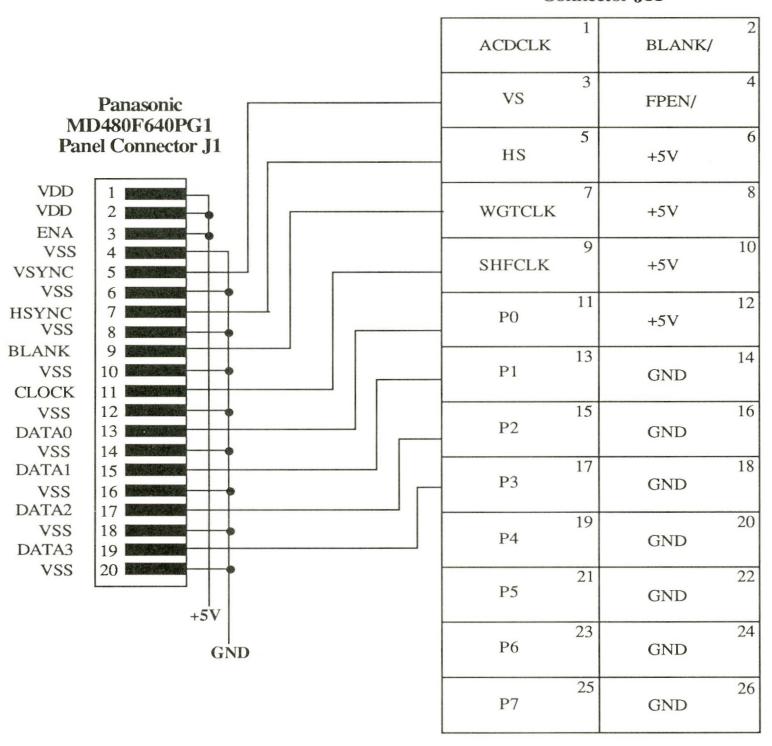

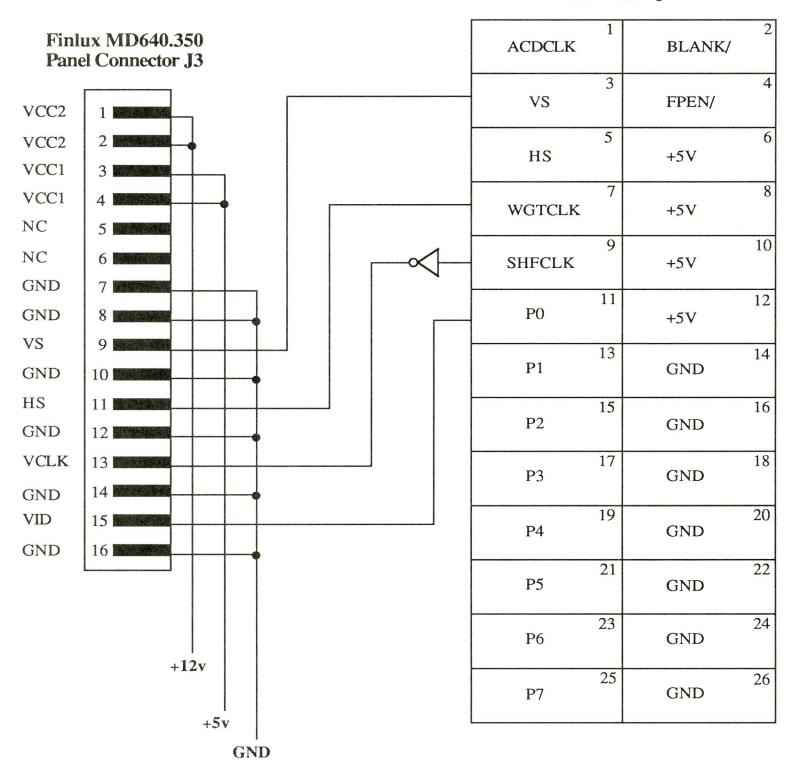

The 82C455 can support the popular panel resolutions of 640x200, 640x350, 640x400 and 640x480. For non-standard applications additional resolutions are supported. The 82C455 provides a direct interface to panels from vendors such as Sharp,

Sanyo, Epson, Oki, Toshiba, Hitachi, Fujitsu, NEC, Matsushita and Finlux.

#### **CRT MONITOR**

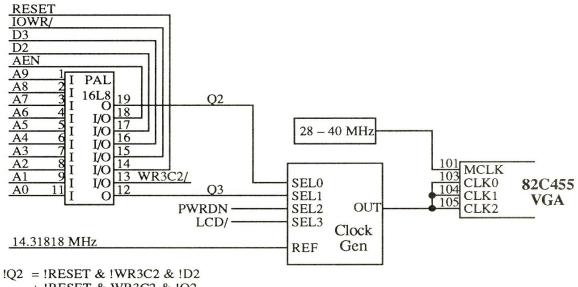

The 82C455 supports both fixed and variable frequency analog monitors, including IBM PS/2<sup>TM</sup> and Multisync<sup>TM</sup> or Multi-Scan monitors. With the addition of a single CMOS PAL and required oscillators, the 82C455 supports digital TTL monitors for CGA, MDA and EGA standards. High resolution support is provided on both fixed and variable frequency monitors. When booting a system, the BIOS determines the monitor type and whether to boot on the CRT or flat panel. Programming a single register switches the display between the CRT and flat panel.

#### **COMPATIBILITY**

The 82C455 is fully compatible with the IBM VGA standard. The 82C455 also provides compatibility with IBM's EGA, CGA and MDA standard and the Hercules graphics adapter. The 82C455 includes a variety of features to provide compatibility on flat panel displays. Internal compensation techniques ensure that industry-standard software designed for different displays can be executed on the single flat panel used in an implementation. Mode initialization is supported at the BIOS and register levels, ensuring compatibility with all application software.

#### **EXTENSION REGISTERS**

The 82C455 employs an "Extension" Register set to control its enhanced features. These Extension Registers provide control of the flat panel interface, flat panel timing, vertical compensation, SMARTMAP<sup>TM</sup> and Backwards Compatibility.

#### **Flat Panel Interface Registers**

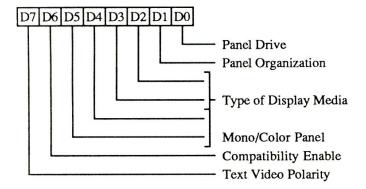

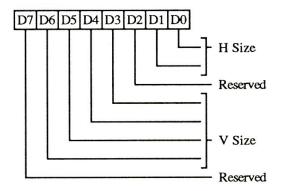

The Flat Panel Interface characteristics are controlled by a subset of the Extension Registers. These Registers select the panel type, data formatting, panel configuration, panel size, clock selection and video polarity. Since the 82C455 is designed to support a wide range of panel types and sizes, the control of these features is fully programmable. The video polarity of text and graphics modes is independently settable to allow black text on a white background and still provide normal graphics images.

# **Flat Panel Timing Registers**

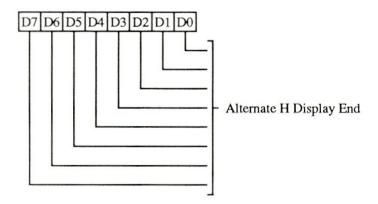

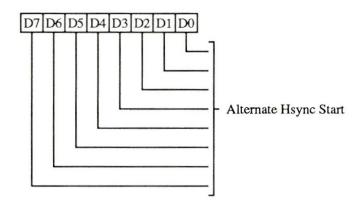

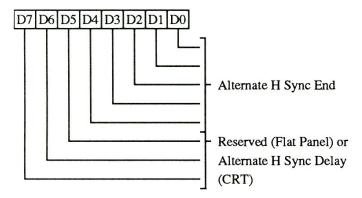

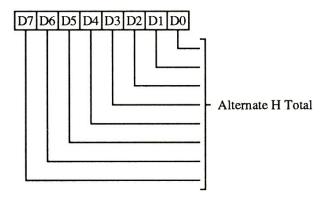

Flat panel displays usually require sync signal timing that is different from a CRT. To provide full compatibility with IBM VGA standard, alternate timing registers are used to allow independent timing of the sync signals for flat panel displays. Unlike the values programmed into the standard CRT timing registers, the value programmed into the alternate timing registers is dependent on the panel type used and is independent of the display mode.

# VERTICAL COMPENSATION

Vertical Compensation is a programmable feature that increases the usable display area when running lower resolution software on a higher resolution panel. Unlike CRT monitors, flat panels have a fixed number of scan lines (e.g., 200, 350, 400 or 480 lines). Lower resolution software run on a higher resolution panel only partially fills the usable display area. For instance, 350-line EGA software displayed on a 480-line panel would leave 130 blank lines at the bottom of the display. The 82C455 offers the following three Vertical Compensation techniques to increase the useable screen area:

First, border insertion (referred to as "centering") adjusts the Display Start and Display End addresses to center the display, leaving a border of unused area at the top and bottom of the panel. Border insertion can be used in text and graphics modes.

Second, line replication (referred to as "stretching") duplicates every Nth display line (where N is programmable), thus stretching text characters and graphic images an adjustable amount. The display can be stretched to completely fill the flat panel area. Double scanning, a form of line replication where every line is replicated, is useful for running 200 line software on a 400 line panel. Line replication can be used in text and graphics modes.

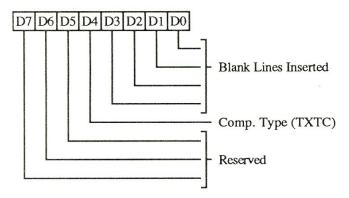

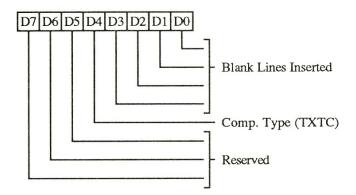

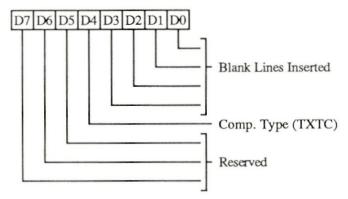

Third, blank line insertion, inserts N blank lines (where N is programmable) between each line of text characters. Thus text can be evenly spaced to fill the entire panel display area without altering the height and shape of the text characters. Blank line insertion can be used in text mode only.

Each of these Vertical Compensation techniques can be controlled by programming the 82C455's Extension Registers. A combination of centering and stretching or blank line insertion may also be used.

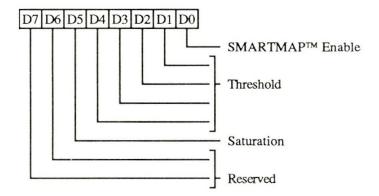

#### **SMARTMAPTM**

SMARTMAP<sup>™</sup> is a proprietary feature that can be invoked to intelligently map colors to gray levels in text mode. SMARTMAP improves the legibility of flat panel displays by solving a common problem:

Most application programs are optimized for color CRT monitors using multiple colors. For example, a word processor might use a blue background with white characters for normal text, underlined text could be display in green, italicized text in yellow, and so on. This variety of colors, which is quite distinct on a color CRT monitor, can be illegible on a monochrome flat panel display if the colors are mapped to adjacent grayscale values. In the example, underlined and italicized text would be illegible if yellow is mapped to grayscale 4, green to grayscale 6 with the blue background mapped to grayscale 5.

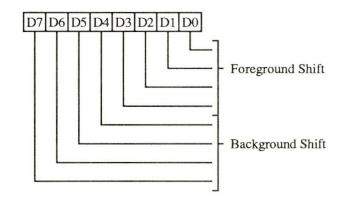

SMARTMAP compares and adjusts the foreground and background grayscale values to produce adequate display contrast on flat panel displays. The minimum contrast value and the foreground/background grayscale adjustment values are programmed in the 82C455's Extension Registers. This feature can also be disabled completely.

# **VIDEO BIOS**

In typical applications, the 82C455 is placed on the CPU board and the video BIOS is integrated with the system BIOS. A signal (ROMCS/) is provided for implementing a separate 8-bit ROM VIDEO BIOS. Chips and Technologies supplies a video BIOS that is optimized for the 82C455 hardware. The BIOS supports the extension functions of the 82C455, such as switching between the flat panel and the CRT, SMARTMAP™, Vertical Compensation, and palette load/save. The BIOS Modification Program (BMP) enables OEMs to tailor their feature set by programming the extension functions. Chips offers the BIOS as a standard production version, a customized version or as source code.

#### **POWER-SAVING MODES**

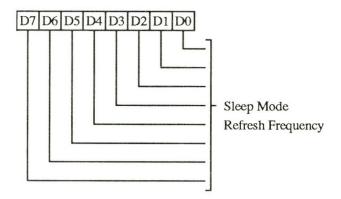

The 82C455 supports two power-down modes to reduce power consumption and extend battery-based operation. The first mode is the Relax mode, during which the display is blanked and the backlight (if used) can be turned off. While in the Relax mode, the 82C455 continues to generate video memory re-

fresh cycles and all display timing signals for the flat panel. The CPU has complete access to all the internal registers and to display memory. This mode is useful when the CPU is manipulating video data and updating display memory but no other user activity is occurring. Because the CRT Controller does not execute any DRAM cycles for the purpose of updating the display, power consumption in the DRAM is reduced. As an added benefit, the CPU can utilize the full display memory bandwidth while in this mode.

The second mode is the Retire mode, during which the 82C455 is invisible to the system. While in the Retire mode, the display is blanked, the display timing signals are halted and the flat panel should be turned off. The CPU cannot access any internal registers or display memory. During Retire, the 82C455 continues to refresh the DRAMs at a programmable rate, to conserve power in the display memory while preventing data loss. This mode is useful when system operation is suspended.

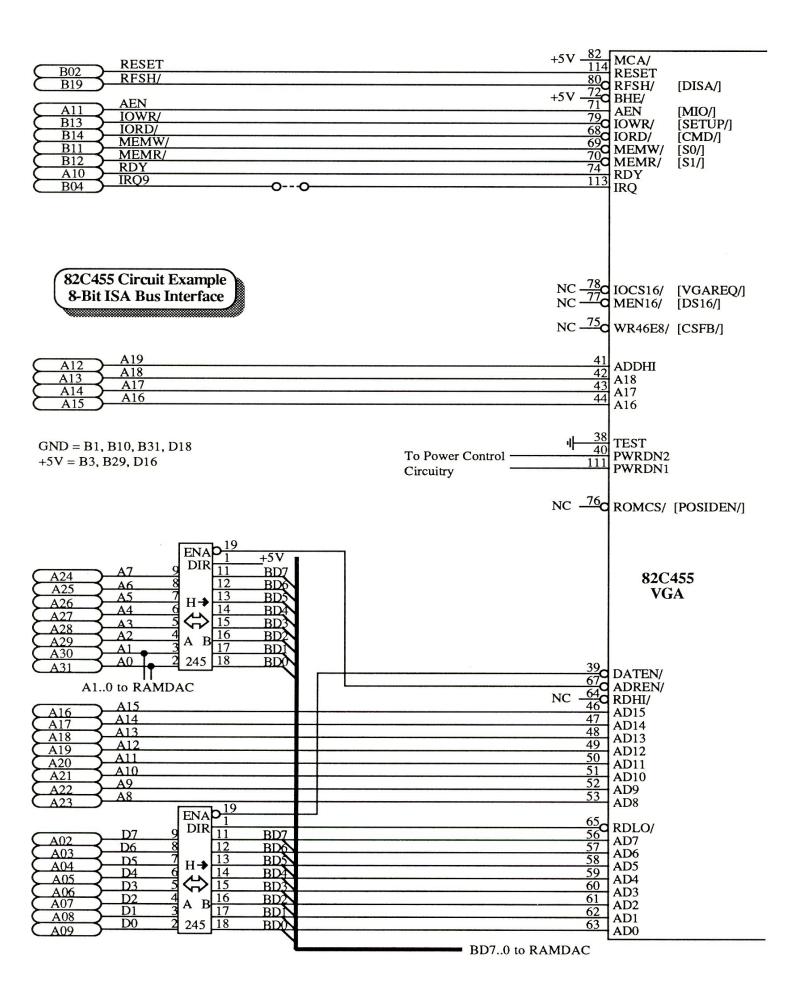

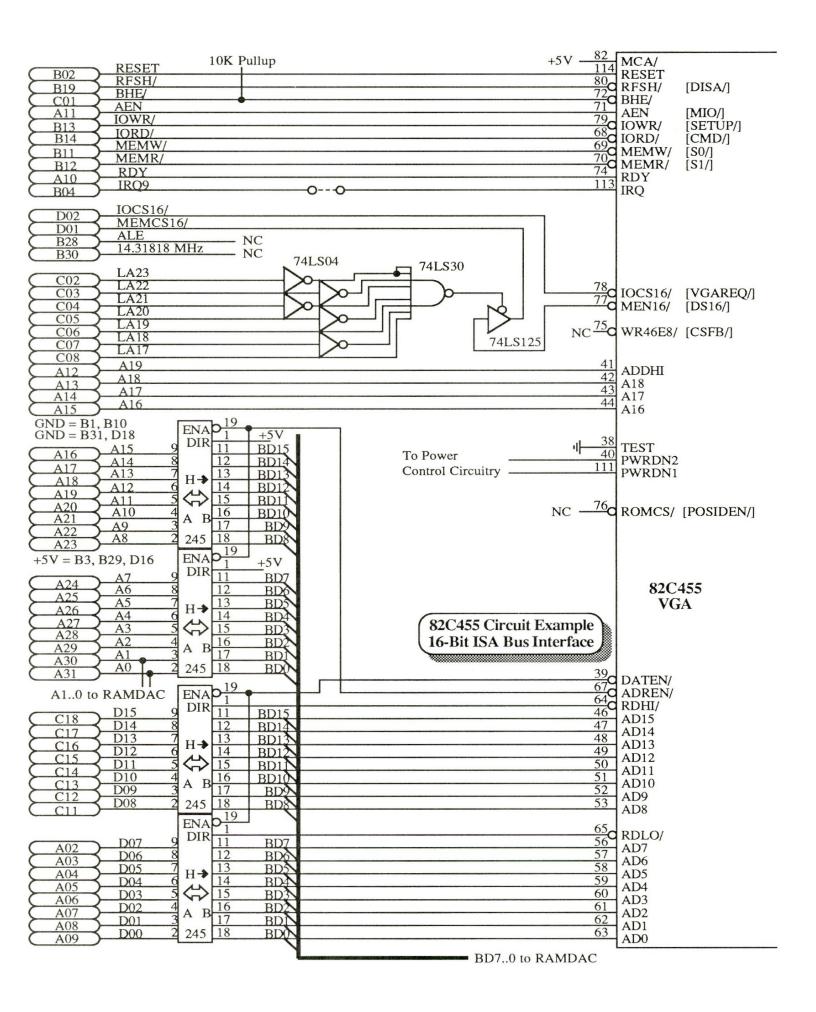

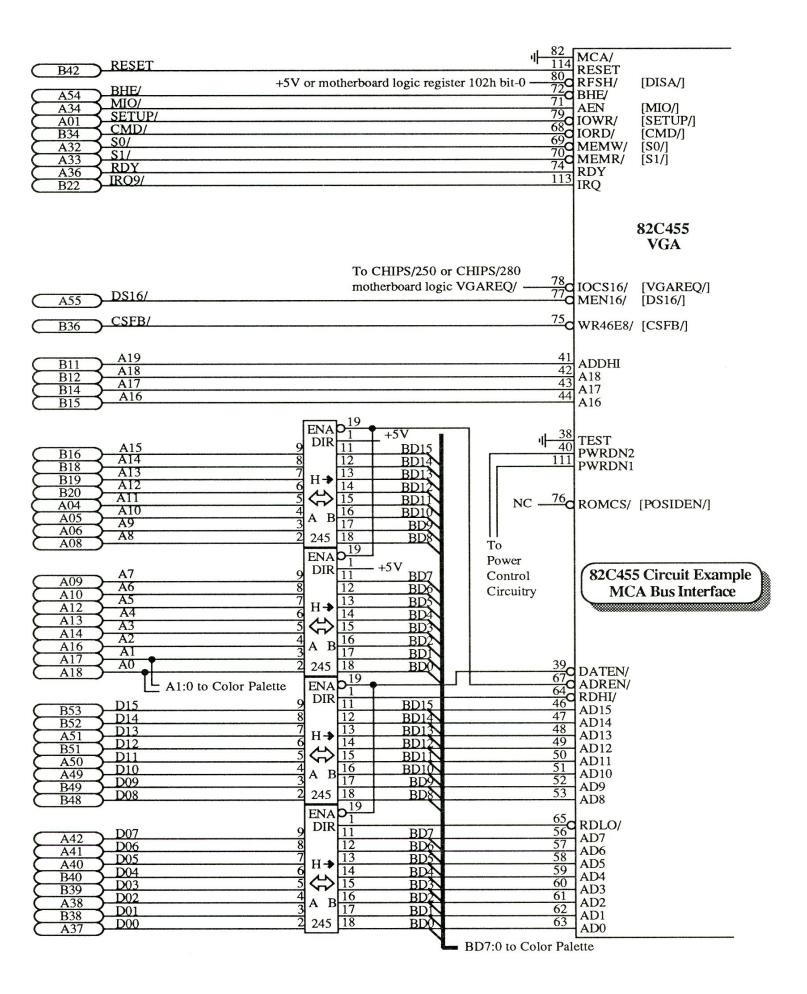

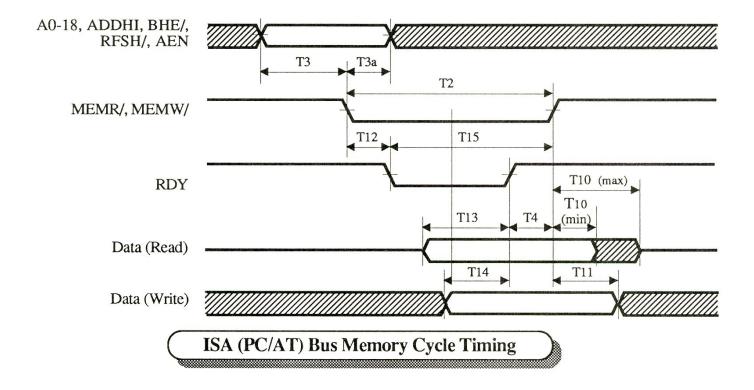

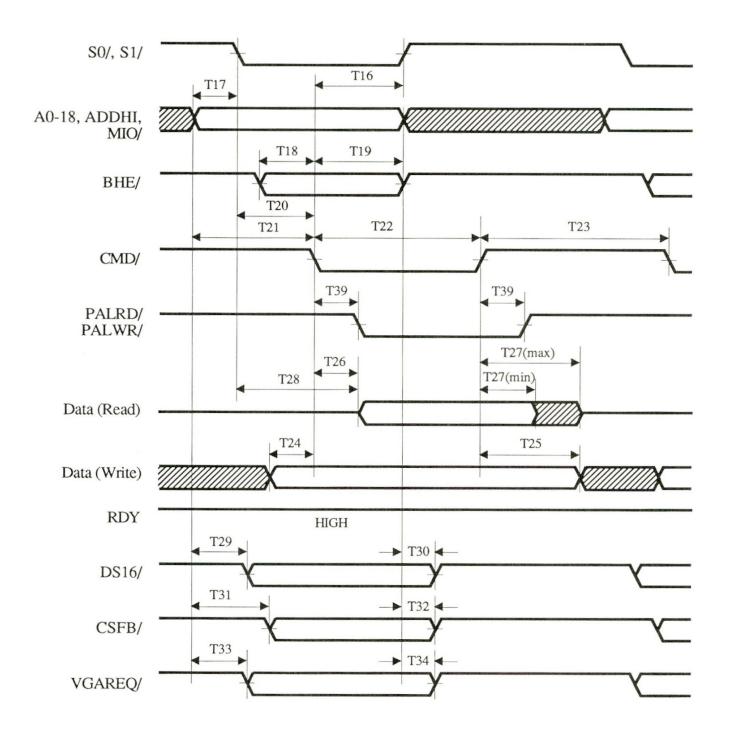

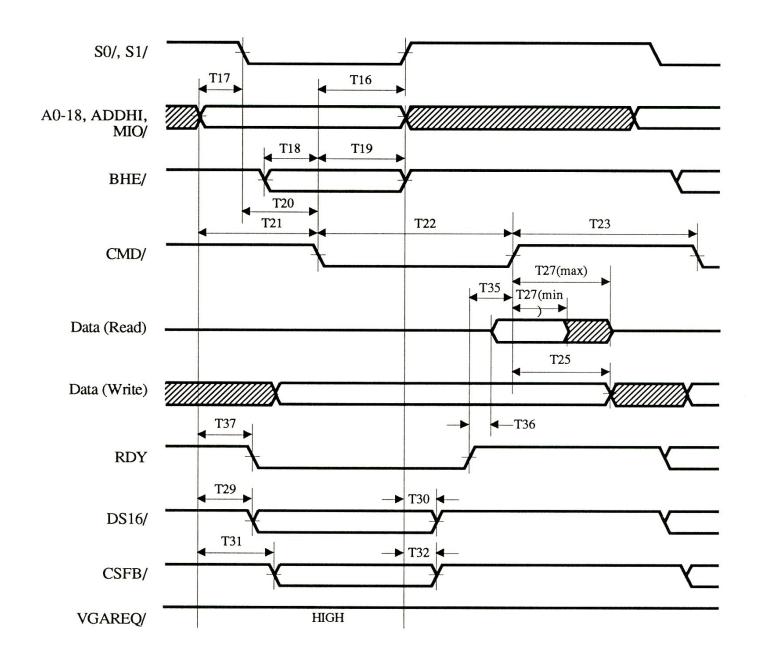

#### **BUS INTERFACE**

The 82C455 directly interfaces to 8-bit PC and PC/XT, 16-bit PC/AT and 8 or 16-bit MCA buses. All operations necessary to ensure proper operation in these various environments are handled in a fashion transparent to the CPU. These include internal decoding of all memory and I/O addresses, bus width translations, and generation of the necessary control signals.

The 82C455 interfaces directly to the CHIPS/250 and CHIPS/280, providing a simple, cost-effective solution for PS/2 compatible systems. When used with one of these CHIPSets, the 82C455 can execute FAST memory cycles at a speed greater than that normally available on the MCA bus.

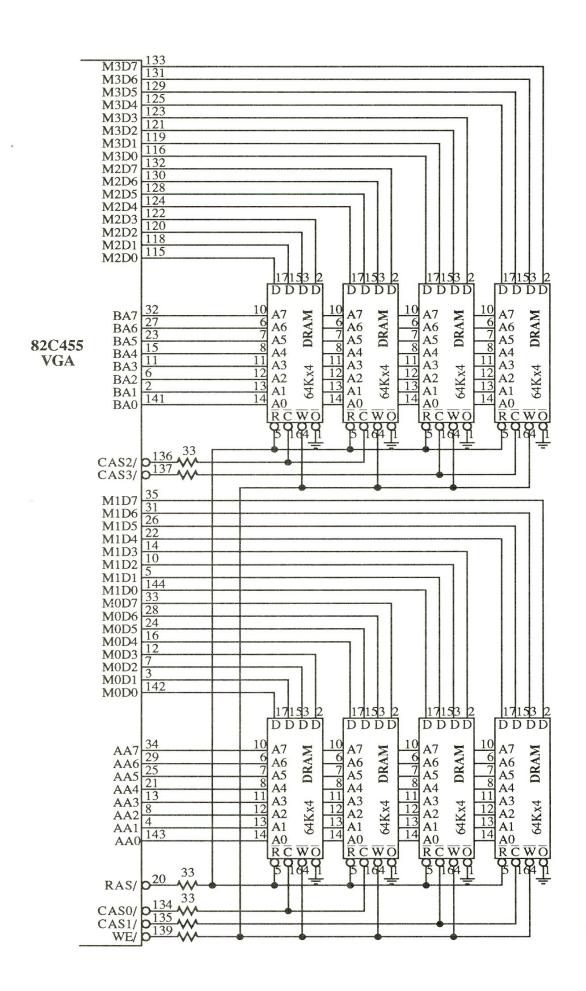

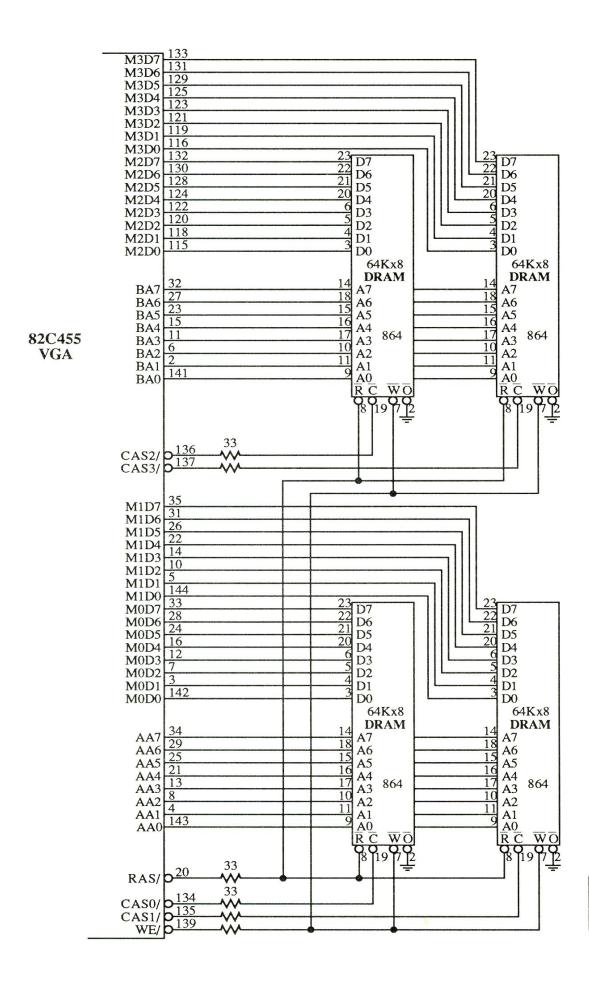

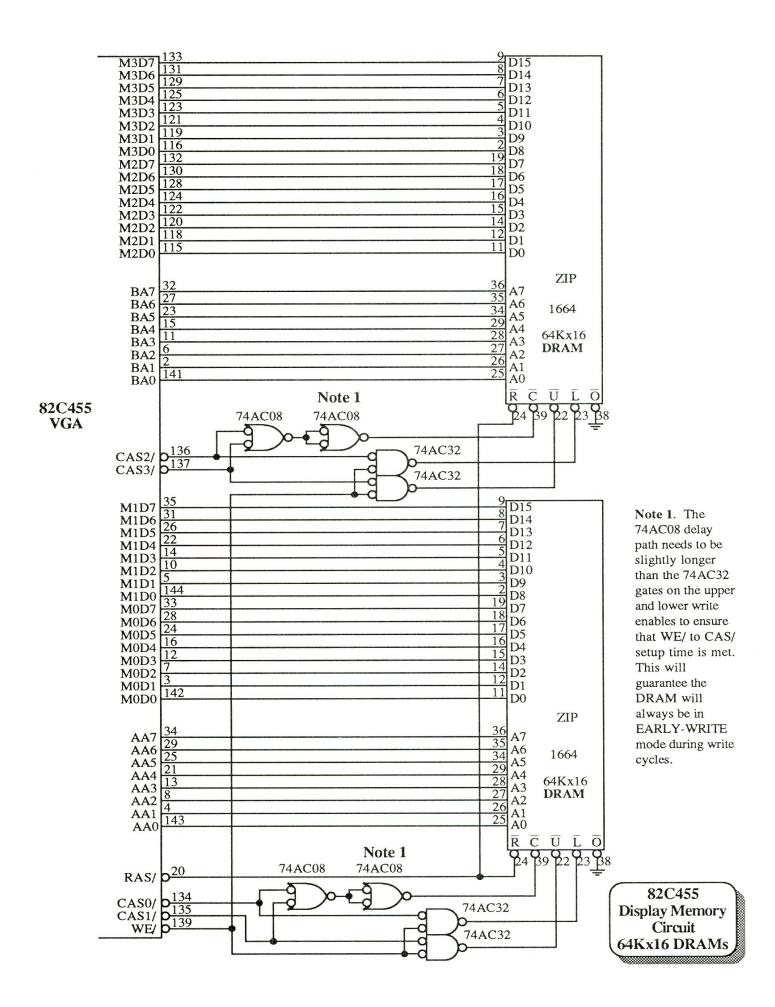

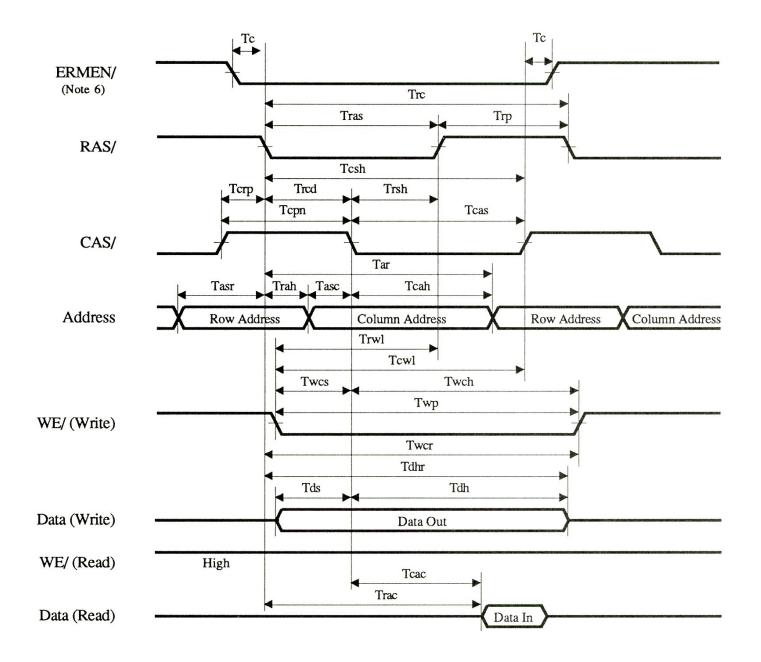

#### **DISPLAY MEMORY**

The 82C455 supports a total of 256 Kbytes of display memory. The 82C455 serves as a DRAM controller for the system's display memory. It handles DRAM refresh, fetches data from display memory as required to refresh the screen, interfaces the CPU to display memory, and supplies all necessary DRAM control signals. The display memory is arranged as four planes of 64 Kbytes each. Each plane is eight bits wide for a total of 32 bits. Planes 0 and 1 share a common address bus, as do Planes 2 and 3. Each plane has a separate CAS signal and share a common RAS and write enable. Supported DRAMS include two 64Kx16 (with separate CAS or write enable signals), four 64Kx8 or eight 64Kx4. 120ns DRAMS are required

for clock inputs up to 30MHz. Pseudo-Static and SRAMs can be supported with external address latches.

# 82C455 ARCHITECTURE

The 82C455 integrates four major internal modules:

# **Graphics Controller**

The Graphics Controller interfaces the 8- or 16-bit CPU data bus to the 32-bit data bus used by the four planes (Maps) of display memory. It also latches and supplies display memory data to the Attribute Controller for use in refreshing the screen image. For text modes, this data is supplied in parallel form (character generator data and attribute code); for graphics modes, it is converted to serial form (one bit from each of four bytes form a single pixel). The Graphics Controller also performs any one of several types of logical operations on data while reading it from or writing it to display memory or the CPU data bus.

# Sequencer

The Sequencer generates all CPU and display memory timing signals. It controls CPU access of display memory by inserting cycles dedicated to CPU access. It also contains mask registers which can prevent writes to individual display memory planes.

# **Attribute Controller**

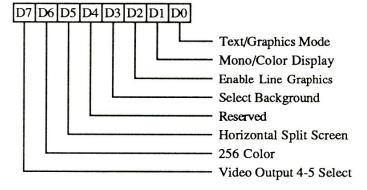

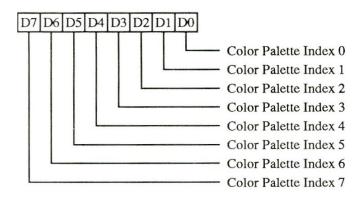

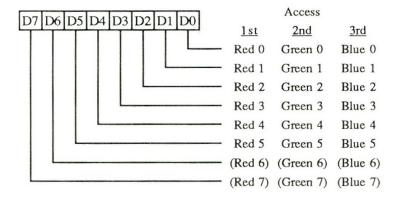

The Attribute Controller generates the 4-bit-wide video data stream used to refresh the display. This is created in text modes from a font pattern and an attribute code which pass through a parallel to serial conversion. In graphics modes, the display memory contains the 4-bit pixel data. In text and 16 color graphic modes the 4-bit pixel data acts as an index into a set of internal color look-up registers which generate a 6-bit stream. Two additional bits of color data are added to provide an 8-bit address to the external color palette. In 256 color modes, two 4-bit values are passed through the color look-up registers and assembled into an 8-bit value. Text and cursor blink, underline and horizontal scrolling are also the responsibility of the Attribute Controller.

#### **CRT Controller**

The CRT Controller generates all the sync and timing signals for the display and also generates the multiplexed row and column addresses used for both display refresh and CPU access of display memory.

#### MODES OF OPERATION

The 82C455 addresses the specific requirements of laptop design by providing different modes of operation to optimize power usage. The table at the bottom of the page summarizes these modes and display memory access in each.

#### **Test Mode**

This mode is entered when the RESET pin is low and the TEST pin is high. It is used for factory test purposes.

#### Reset mode

When this mode is activated by pulling the RESET pin high, the 82C455 is forced to VGA-compatible mode and the CRT is selected as the active display. In addition, the 82C455 is disabled; it must be enabled after deactivating the RESET pin by writing to the Global Enable Register (102h in Setup Mode). Access to all Extension Registers is also disabled. They must be explicitly enabled via the Extension Enable Register (103h in Setup Mode) following a reset. The RESET pin must be active for at least 64 clock cycles.

# Setup Mode

In this mode, only the configuration registers are accessible (these include the Global Enable, Extension Enable and Global ID). In an MCA configuration, Setup mode is entered when the SETUP/ pin is low. This pin is typically controlled by bit-5 of port 94h and is implemented in system logic external to the 82C455. In a PC-bus implementation, Setup mode is entered by writing a 1 to bit-4 of port 46E8h. This port is incorporated in the 82C455. While in Setup mode, the video output is active if it was active prior to entering Setup mode

and inactive if it was inactive prior to entering Setup mode.

# Normal Operating Mode

In this mode all functions of the 82C455 are enabled except that the configuration registers are not accessible.

#### Relax and Retire Modes

The 82C455 supports two power-down modes to reduce power consumption and extend battery-based operation. The first mode is the Relax mode, during which the display is blanked and the backlight (if used) can be turned off. While in the Relax mode, the 82C455 continues to generate video memory refresh cycles and all display timing signals for the flat panel. The CPU has complete access to all the internal registers and to display memory. This mode is useful when the CPU is manipulating video data and updating display memory but no other user activity is occurring. Because the CRT Controller does not execute any DRAM cycles for the purpose of updating the display, power consumption in the DRÂM is reduced. As an added benefit, the CPU can utilize the full display memory bandwidth while in this mode.

The second mode is the Retire mode, during which the 82C455 is invisible to the system. While in the Retire mode, the display is blanked, the display timing signals are halted and the flat panel should be turned off. The CPU cannot access any internal registers or display memory. During Retire, the 82C455 continues to refresh the DRAMs at a programmable rate to conserve power in the display memory while preventing data loss. This mode is useful when system operation is suspended.

| Mode of<br>Operation | RESET<br>Pin | TEST<br>Pin | PWRDN1<br>Pin | PWRDN2<br>Pin | Display Memory<br>Access<br>by CPU | Display Memory<br>Access for<br>Display Refresh |

|----------------------|--------------|-------------|---------------|---------------|------------------------------------|-------------------------------------------------|

| Test                 | Low          | High        | XXX           | XXX           |                                    |                                                 |

| Reset                | High         | XXX         | XXX           | XXX           |                                    |                                                 |

| Setup                |              |             |               |               | No                                 | Yes                                             |

| Normal               | Low          | Low         | Low           | Low           | Yes                                | Yes                                             |

| Relax                | Low          | Low         | High          | Low           | Yes                                | No                                              |

| Retire               | Low          | Low         | Low           | High          | No                                 | No                                              |

Note: Combinations of pin levels not shown in the table above are illegal and should not be used.

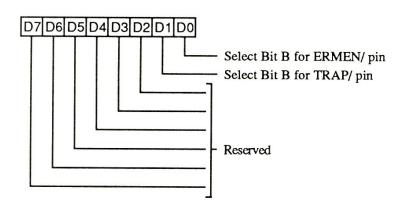

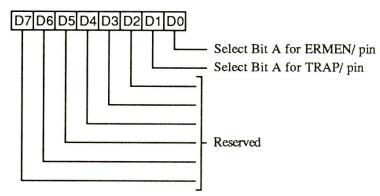

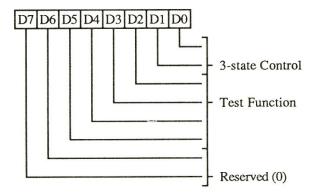

#### GENERAL PURPOSE OUTPUTS

The 82C455 provides two general purpose output pins. This feature relies on redefinition of the TRAP/ and ERMEN/ pins with the General Purpose Output Registers (XR08 and XR09). These pins can be defined to serve their normal function or can be individually 3-stated, forced low, or forced high. In most applications, the trap pin is used as a CRT / LCD control signal.

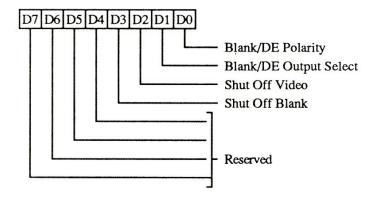

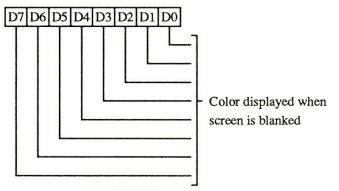

#### SCREEN BLANKING

The 82C455 permits blanking of the display by writing to bit-5 of the Sequencer Clocking Mode Register (SR01) or by pulling the PWRDN1 pin high. With the screen blanked, all memory cycles are available to the CPU except those used for display memory refresh. In addition, the video output can be forced to a pre-defined color (the default video) whenever the BLANK/ pin is asserted. This color is written to the Default Video Register (XR2B) (an Extension Register).

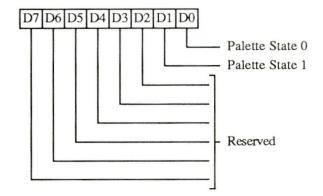

#### INTERNAL AND EXTERNAL PALETTES

The 82C455 contains 16 color look-up registers (in the Attribute Controller), each of which is 6 bits wide. These are used in 16 color modes to select 16 active colors from a palette of 64.

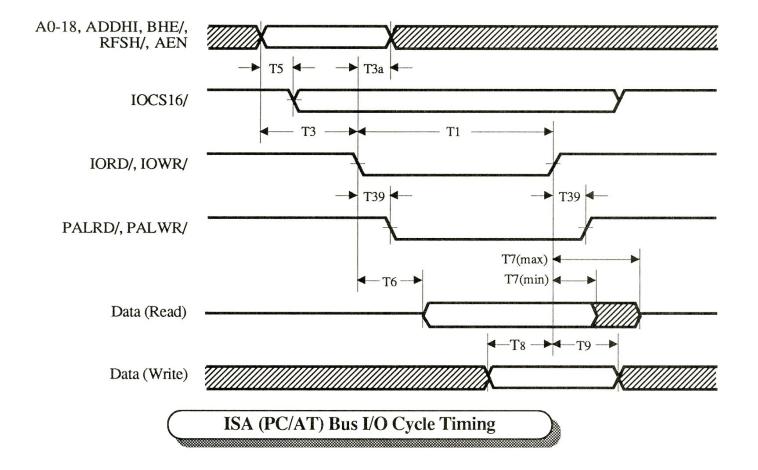

The 82C455 also supports an external palette DAC (Inmos IMSG176 or equivalent). CPU access to this device is controlled by the 82C455, which decodes CPU accesses and generates the PALRD/ and PALWR/ signals for the external palette. I/O addresses 3C6-3C9h are valid external palette addresses.

The internal color look-up table is always used in CRT modes and can be optionally used in the flat panel modes. The external palette is used only with analog CRTs. It is not used with digital CRTs and flat panels.

# LIGHT PEN REGISTERS

In the CGA and Hercules modes, the contents of the Display Address counter are saved at the end of the frame before being reset. The saved value can be

read in the CRT Controller Register space at indices 10h and 11h. This allows simulation of a light pen hit in CGA and Hercules modes.

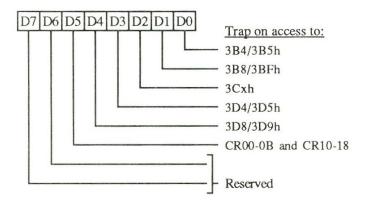

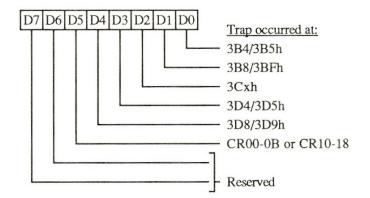

#### SYSTEM TRAPS

The 82C455 supports generation of traps (NMIs) on one or more conditions. The Trap Enable and Trap Status Registers (XR16 and XR17) are utilized to implement this feature. Note: the use of traps with OS/2™ and other operating environments may cause problems.

#### FRAME INTERRUPTS

The 82C455 supports frame interrupts in a manner compatible to either the PC bus or MCA bus. For compatibility with the IBM VGA adapter in the PC bus, frame interrupts may also be disabled through the Emulation Mode register (XR14).

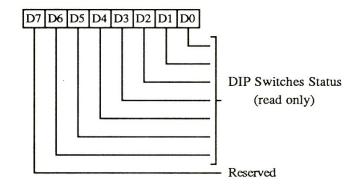

#### **DIP SWITCH INPUTS**

The 82C455 supports up to 7 DIP switch inputs. These can be read through the Dip Switch Register (XR01). To implement this feature, the A16, A17, A18, BHE/, ADDHI, AEN (MIO/) and RFSH/ (VGAENAB) pins are connected to the 7 DIP switches through a multiplexer. These inputs can be used to define initialization conditions. Note: the standard CHIPS BIOS does not require that any DIP switches be connected to these inputs.

#### **CONTEXT SWITCHING**

For support of multi-tasking, windowing and context switching operating environments, the entire state of the 82C455 (internal registers) is read- and write-able. This feature is 100% compatible with IBM's VGA.

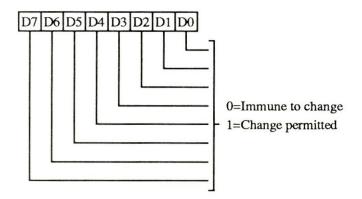

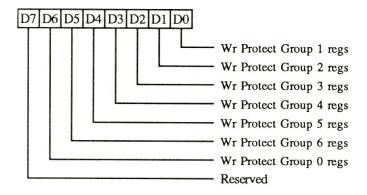

#### WRITE PROTECTION

A Feature of the 82C455 is the ability to write protect most of the standard VGA registers. This feature is used to provide backwards compatibility with software written for older generation display types. The write protection is grouped into register sets and controlled by the Write Protect Register (XR15).

| Pin# | Pin Name |           | Туре | Active | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|----------|-----------|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 71   | AEN      | [MIO/]    | In   | Both   | ADDRESS ENABLE or MEMORY/IO and AUXILIARY DATA BIT 5. In PC-Bus interfaces, this input is named AEN. When low, it indicates a valid I/O address. In MCA interfaces, MIO/ high selects a memory cycle and low selects an I/O cycle. When defined as MIO/, it must be valid when the ADREN/ input is low. The AEN [MIO/] signal is latched internally. In both MCA and PC-Bus environments this pin serves as an auxiliary data bit input. It is read into bit 5 of the DIP Switch register whenever the DIP Switch register is accessed by the CPU. |

| 69   | MEMW/    | [S0/]     | In   | Low    | MEMORY WRITE or STATE 0/. In PC-Bus interface applications, this input is named MEMW/. It must be low for CPU writes to display memory. S0/ is the memory and I/O write input from the MCA bus.                                                                                                                                                                                                                                                                                                                                                    |

| 70   | MEMR/    | [S1/]     | In   | Low    | MEMORY READ or STATE 1/. In PC-Bus interface applications, this input must be low to permit the CPU to read display memory. S1/ is the memory and I/O read input from the MCA bus.                                                                                                                                                                                                                                                                                                                                                                 |

| 79   | IOWR/    | [SETUP/]  | In   | Low    | I/O WRITE or VGA SETUP. In PC-BUS interface applications, this input is named IOWR/. It must be low to permit the CPU to write to an 82C455 I/O register. In an MCA environment the active low SETUP/ input allows configuration registers at I/O Addresses 100-104h to be accessed. All other memory and I/O functions are disabled.                                                                                                                                                                                                              |

| 68   | IORD/    | [CMD/]    | In   | Low    | I/O READ or VGA COMMAND. In a PC-Bus environment this input is named IORD/. It must be low to permit the CPU to read an I/O register. In an MCA environment this active low signal indicates a command bus cycle. CMD/ must not be asserted during system memory refresh cycles.                                                                                                                                                                                                                                                                   |

| 80   | RFSH/    | [VGAENAB] | In   | Both   | REFRESH or VGA ENABLE and AUXILIARY DATA BIT 6. In the PC-Bus interface, RFSH/ high indicates a valid memory cycle. In an MCA environment this active high input signal enables memory and I/O accesses. This pin also serves as an auxiliary data bit input which is read into bit 6 of the DIP Switch register whenever the DIP Switch register is accessed by the CPU.                                                                                                                                                                          |

| 82   | PTMC     | [MCA/]    | In   | Both   | PTMC. This input selects the type of CPU interface. PTMC low selects an MCA interface and high selects a PC-Bus (ISA) interface. This input must always be valid.                                                                                                                                                                                                                                                                                                                                                                                  |

| Pin# | Pin Name |                     | Type | Active | Description                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|------|----------|---------------------|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 78   | IOCS16/  | [VGAREQ/]           | Out  | Low    | I/O SELECT 16 or VGA REQUEST. In a PC-Brenvironment this active low signal indicates a validabit I/O cycle. IOCS16/ is driven when the VGA accessed and 3-stated when the VGA is inactive. In a MCA environment this output indicates that a FAS memory cycle can be executed. (This feature can lidisabled through a register).                                                                         |  |  |

| 74   | RDY      | (DS16/)<br>(DGARDY) | Out  | High   | VGA READY. When low, this output indicates that the current CPU read/write cycle must be extended with wait states. RDY is driven when the VGA is accessed; it is 3-stated when the VGA is inactive.                                                                                                                                                                                                     |  |  |

| 77   | MEN16/   | [DS16]              | Out  | Low    | MEMORY ENABLE 16 or VGA ADDRESS SELECT 16. In a PC-Bus environment this active low signal indicates 16-bit memory cycle transfers are enabled. This signal should be used by external logic to enable decode of high order addresses and generation of MEMCS16/ for the PC-AT bus. In an MCA environment this active low output indicates that a 16-bit memory or I/O transfer cycle is occurring.       |  |  |

| 75   | WR46E8/  | [CSFB/]             | Out  | Low    | WRITE 46E8h or CARD SELECT FEEDBACK (VGA Acknowledge). In a PC-Bus environment this active low signal indicates a valid I/O write to address 46E8h. In an MCA environment this active low output indicates a valid CPU access (memory or I/O) to the 82C455.                                                                                                                                             |  |  |

| 76   | ROMCS/   |                     | Out  | Low    | ROM CHIP Select. In a PC-Bus environment this active low signal indicates a valid memory read in the range C0000h-C7FFFh. It is used to generate the enable for 8-bit BIOS ROMs.                                                                                                                                                                                                                         |  |  |

| 113  | IRQ      | [IRQ/]              | Out  | Both   | VGA INTERRUPT. An interrupt can be generated whenever the vertical sync signal goes active. For the PC-Bus, this pin may be logically disconnected (3-stated) through the Emulation Mode register (XR14D7) independent of whether interrupts are enabled or disabled. Clearing XR14D7 emulates the function of the IBM PC-Bus VGA board interrupt output. In the MCA bus, this pin is always functional. |  |  |

|      |          | ,                   |      |        | Interrupt State PC Bus MCA Bus XR14D7=1 Disabled 3-state 3-state Enabled & Inactive Enabled & Active 3-state Low High                                                                                                                                                                                                                                                                                    |  |  |

| Pin#      | Pin Name         | Туре     | Active       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------|------------------|----------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 114       | RESET            | In       | High         | RESET. An active high input which resets the 82C455.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 38        | TEST             | In       | High         | TEST. This input is used for factory testing only. It must be tied low for normal operation.                                                                                                                                                                                                                                                                                                                                                                                                 |

| 40<br>111 | PWRDN2<br>PWRDN1 | In<br>In | High<br>High | POWER DOWN 2,1. The Power Down input pins select the Normal, Relax, and Retire modes of operation as follows:                                                                                                                                                                                                                                                                                                                                                                                |

|           |                  |          |              | PWRDN2 PWRDN1 Operation 0 0 Normal Operation 0 1 Relax Mode 1 0 Retire Mode 1 1 Illegal                                                                                                                                                                                                                                                                                                                                                                                                      |

| 108       | SENSE            | In       | Both         | SENSE. The state of this input pin can be read at Input Status Register 0, Bit 4.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 100       | PALRD/           | Out      | Low          | PALETTE READ. This output is active low during I/O reads from addresses in the range 3C6h or 3C8-3C9h (I/O reads from 3C7h are handled directly by the 82C455). This output is normally connected to the Read input of an external Palette/DAC (Brooktree BT475 or equivalent).                                                                                                                                                                                                              |

| 99        | PALWR/           | Out      | Low          | PALETTE WRITE. This output is active low during I/O writes to addresses in the range 3C6-3C9h and is normally connected to the Write input of an external Palette/DAC (Brooktree BT475 or equivalent).                                                                                                                                                                                                                                                                                       |

| 41        | ADDHI            | In       | High         | ADDRESS HIGH and AUXILIARY DATA BIT 4. This high order memory address enable input is generated external to the 82C455 by decoding system addresses A19-A23. As an address, it must be valid when ADREN/ is low, is latched internally and specifies that the current memory address is valid for the 82C455. This pin is an auxiliary data bit read into bit 4 of the DIP Switch register when the DIP Switch register is accessed by the CPU. This input pin is ignored during I/O cycles. |

| 72        | ВНЕ/             | In       | Low          | BYTE HIGH ENABLE and AUXILIARY DATA BIT 3. BHE/ low indicates that the high order byte at the current word address is being accessed. If active, BHE/ must be valid when ADREN/ is low. This pin is also an auxiliary data input which is read into bit 3 of the DIP Switch register when the DIP Switch register is accessed by the CPU. This data bit is latched internally on the falling edge of the command signal.                                                                     |

| Pin#                                                                                         | Pin Name                                                                                                           | Туре                                    | Active                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 67                                                                                           | ADREN/                                                                                                             | Out                                     | Low                                     | ADDRESS ENABLE. The ADREN/ output controls external multiplexing of the system address/data bus. ADREN/ low selects address and ADREN/ high selects data. In a PC or PC/AT bus interface, ADREN/ is low when MEMR/, MEMW/, IORD/, and IOWR/ are all high. ADREN/ is high when any one of MEMR/, MEMW/, IORD/ or IOWR/ is low. In an MCA interface, ADREN/ is low when CMD/ is high and ADREN/ is high when CMD/ is low. |

| 39                                                                                           | DATEN/                                                                                                             | Out                                     | Low                                     | DATA ENABLE. Inverse of ADREN/. This pin is 3-stated during RESET.                                                                                                                                                                                                                                                                                                                                                      |

| 65                                                                                           | RDLO/                                                                                                              | Out                                     | Low                                     | READ LOW. This output controls the direction of the external data transceivers on the low order byte (Bits 0-7) of the address/data bus. It is low when data is read from the 82C455 and high when data is written to the 82C455. DATEN/ can be used to enable the external transceiver. This pin is 3-stated during RESET.                                                                                             |

| 64                                                                                           | RDHI/                                                                                                              | Out                                     | Low                                     | READ HIGH. This output operates identically to the RDLO/ output except that it controls the direction for the high order byte (Bits 8-15) of the address/data bus. RDHI/ is low when data is read from the 82C455 and high when data is written to the 82C455. This pin is 3-stated during RESET.                                                                                                                       |

| 63<br>62<br>61<br>60<br>59<br>58<br>57<br>56<br>53<br>52<br>51<br>50<br>49<br>48<br>47<br>46 | AD0<br>AD1<br>AD2<br>AD3<br>AD4<br>AD5<br>AD6<br>AD7<br>AD8<br>AD9<br>AD10<br>AD11<br>AD12<br>AD13<br>AD14<br>AD15 | I/O | Both Both Both Both Both Both Both Both | SYSTEM ADDRESS and DATA BITS 15-0. These bits are used to address display memory and the I/O mapped 82C455 internal registers. They also transfer data between the CPU bus and display memory and 82C455 registers. Addresses must be valid when output signal ADREN/ is low and data must be held while DATEN/ is low. Addresses are latched internally.                                                               |

| 44<br>43<br>42                                                                               | A16<br>A17<br>A18                                                                                                  | In<br>In<br>In                          | Both<br>Both<br>Both                    | SYSTEM ADDRESS BITS 18-16 and AUXILIARY DATA BITS 2-0. These bits transfer a high-order address when ADREN/ is low. The auxiliary data bits on pins A16, A17, and A18 respectively are read into bits 0-2, respectively, of the DIP Switch register when that register is accessed by the CPU. The address bits are latched internally and are ignored for I/O cycles.                                                  |

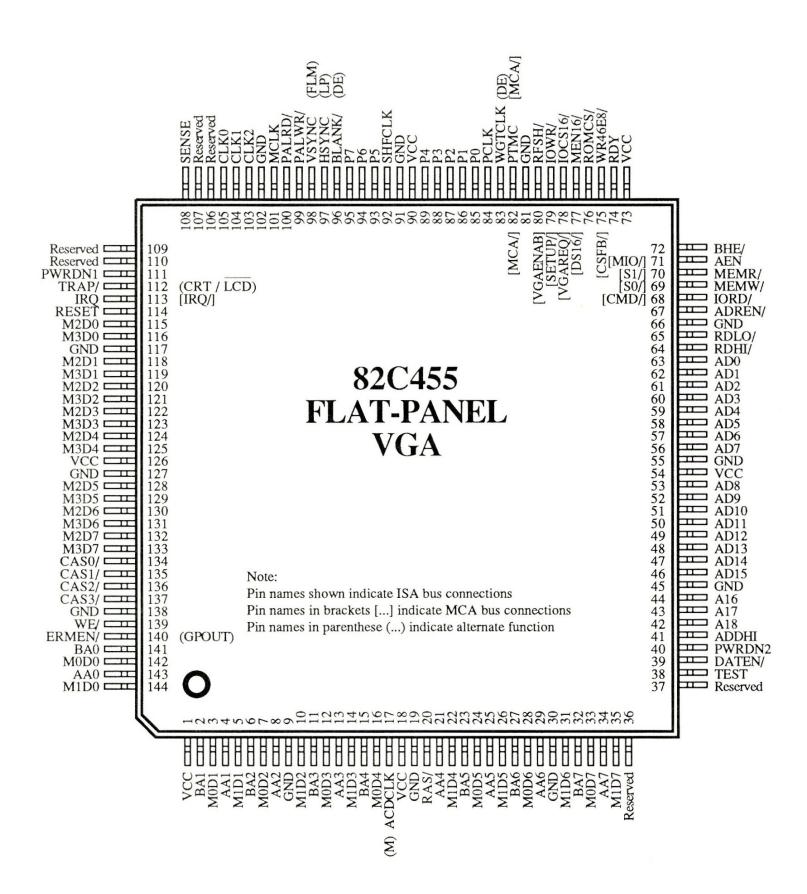

# 82C455 PIN DESCRIPTIONS

| Pin#                                                 | Pin Name                                                     | Туре                                          | Active                                               | Description                                                 |

|------------------------------------------------------|--------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------|-------------------------------------------------------------|

| 142<br>3<br>7<br>12<br>16<br>24<br>28<br>33          | M0D0<br>M0D1<br>M0D2<br>M0D3<br>M0D4<br>M0D5<br>M0D6<br>M0D7 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | Both<br>Both<br>Both<br>Both<br>Both<br>Both<br>Both | MEMORY 0 DATA. Display memory data bus for Plane 0 (Map 0). |

| 144<br>5<br>10<br>14<br>22<br>26<br>31<br>35         | M1D0<br>M1D1<br>M1D2<br>M1D3<br>M1D4<br>M1D5<br>M1D6<br>M1D7 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | Both<br>Both<br>Both<br>Both<br>Both<br>Both<br>Both | MEMORY 1 DATA. Display memory data bus for Plane 1 (Map 1). |

| 115<br>118<br>120<br>122<br>124<br>128<br>130<br>132 | M2D0<br>M2D1<br>M2D2<br>M2D3<br>M2D4<br>M2D5<br>M2D6<br>M2D7 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | Both<br>Both<br>Both<br>Both<br>Both<br>Both<br>Both | MEMORY 2 DATA. Display memory data bus for Plane 2 (Map 2). |

| 116<br>119<br>121<br>123<br>125<br>129<br>131<br>133 | M3D0<br>M3D1<br>M3D2<br>M3D3<br>M3D4<br>M3D5<br>M3D6<br>M3D7 | I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O<br>I/O | Both<br>Both<br>Both<br>Both<br>Both<br>Both<br>Both | MEMORY 3 DATA. Display memory data bus for Plane 3 (Map 3). |

| Pin# | Pin Name | Туре | Active | Description                                                                       |

|------|----------|------|--------|-----------------------------------------------------------------------------------|

| 143  | AA0      | Out  | Both   | ADDRESS PLANES 1,0. Display memory address                                        |

| 4    | AA1      | Out  | Both   | bus for DRAM planes 0 and 1.                                                      |

| 8    | AA2      | Out  | Both   |                                                                                   |

| 13   | AA3      | Out  | Both   |                                                                                   |

| 21   | AA4      | Out  | Both   |                                                                                   |

| 25   | AA5      | Out  | Both   |                                                                                   |

| 29   | AA6      | Out  | Both   |                                                                                   |

| 34   | AA7      | Out  | Both   |                                                                                   |

| 141  | BA0      | Out  | Both   | ADDRESS PLANES 3,2 Display memory address bus                                     |

| 2    | BA1      | Out  | Both   | for DRAM Planes 2 and 3.                                                          |

| 6    | BA2      | Out  | Both   |                                                                                   |

| 11   | BA3      | Out  | Both   |                                                                                   |

| 15   | BA4      | Out  | Both   |                                                                                   |

| 23   | BA5      | Out  | Both   |                                                                                   |

| 27   | BA6      | Out  | Both   |                                                                                   |

| 32   | BA7      | Out  | Both   |                                                                                   |

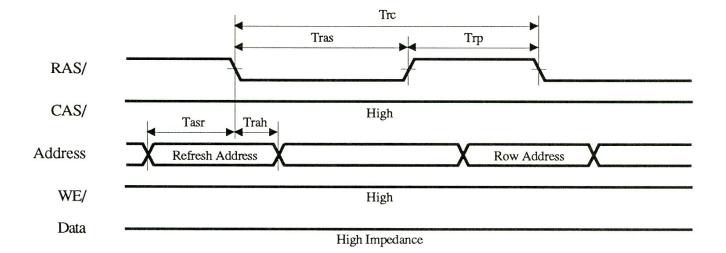

| 20   | RAS/     | Out  | Low    | ROW ADDRESS STROBE. Row address strobe for all DRAM memory banks.                 |

| 134  | CAS0/    | Out  | Low    | COLUMN ADDRESS STROBE 0. Active low column address strobe for Memory Plane 0.     |

| 135  | CAS1/    | Out  | Low    | COLUMN ADDRESS STROBE 1. Active low column address strobe for Memory Plane 1.     |

| 136  | CAS2/    | Out  | Low    | COLUMN ADDRESS STROBE 2. Active low column address strobe for Memory Plane 2.     |

| 137  | CAS3/    | Out  | Low    | COLUMN ADDRESS STROBE 3. Active low column address strobe for Memory Plane 3.     |

| 139  | WE/      | Out  | Low    | WRITE ENABLE. Active low write enable signal for all display memory banks/planes. |

# **82C455 PIN DESCRIPTIONS**

| Pin#                                         | Pin Name                               |       | Туре                                    | Active                                               | Description                                                                                                                                                                                                                                                                                                  |

|----------------------------------------------|----------------------------------------|-------|-----------------------------------------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

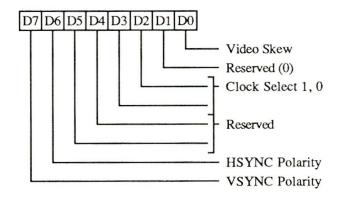

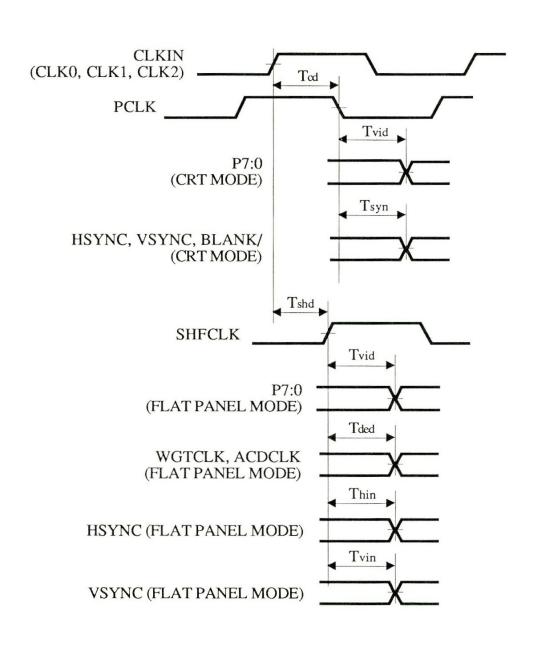

| 97                                           | HSYNC                                  | (LP)  | Out                                     | Both                                                 | HORIZONTAL SYNC OUTPUT. HSYNC is active high if the horizontal polarity bit (Bit-6 of the Misc. Output register, 3C2h) is low. It is active low if the horizontal polarity bit is high. In flat panel mode the polarity is controlled by the Alt. Misc. Output Reg. (XR54).                                  |

| 98                                           | VSYNC                                  | (FLM) | Out                                     | Both                                                 | VERTICAL SYNC OUTPUT. VSYNC is active high if the vertical polarity bit (Bit 7 of the Misc. Output register, 3C2h) is low. It is active low if the vertical polarity bit is high. In flat panel mode the polarity is controlled by the Alt. Misc. Output Reg. (XR54).                                        |

| 96                                           | BLANK/                                 | (DE)  | Out                                     | Both                                                 | BLANK or DISPLAY ENABLE. BLANK/ is a programmable output for blanking the CRT which is normally connected to the RAMDAC. It can be redefined as a Display Enable signal in systems where a RAMDAC is not required.                                                                                           |

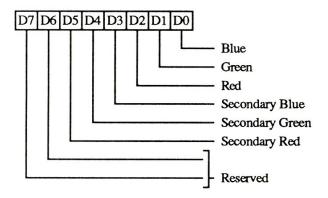

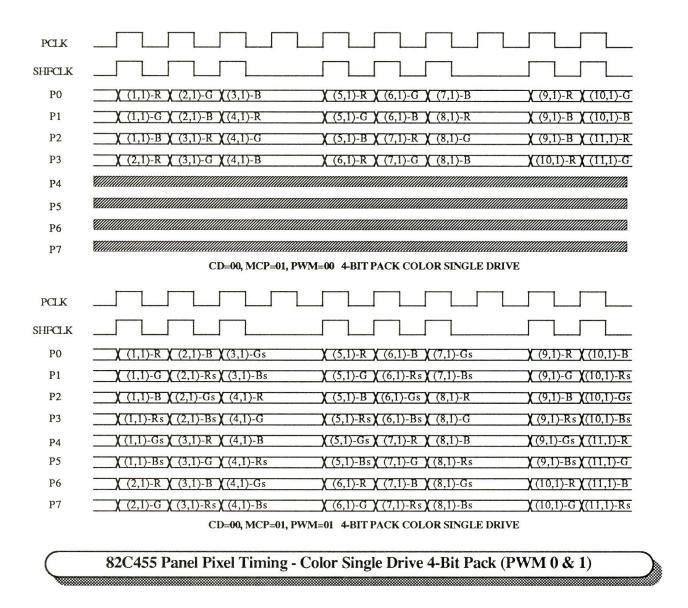

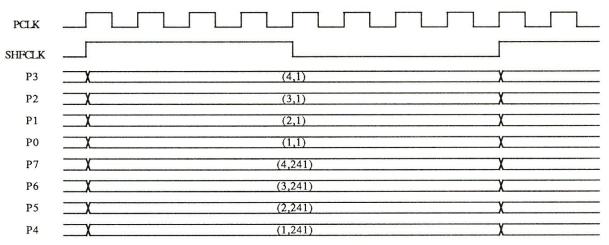

| 85<br>86<br>87<br>88<br>89<br>93<br>94<br>95 | P0<br>P1<br>P2<br>P3<br>P4<br>P5<br>P6 |       | Out | Both<br>Both<br>Both<br>Both<br>Both<br>Both<br>Both | VIDEO PIXEL DATA 7-0. Eight outputs to drive color or monochrome display devices. Color values for digital CRT interface are assigned as follows:  PO B Blue P1 G Green P2 R Red P3 BS/V Secondary Blue / Monochrome P4 GS/I Secondary Green / Intensity P5 RS Secondary Red P6 User Defined P7 User Defined |

| 92                                           | SHFCLK                                 |       | Out                                     | Both                                                 | SHIFT CLOCK. Output pixel clock to which video panel output data is synchronized.                                                                                                                                                                                                                            |

| 84                                           | PCLK                                   |       | Out                                     | Both                                                 | PIXEL CLOCK. Output pixel clock to which CRT Video output data is synchronized. This pin is 3-stated during RESET.                                                                                                                                                                                           |

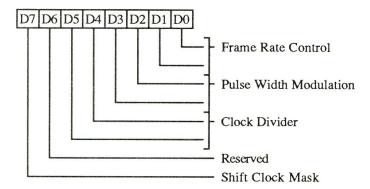

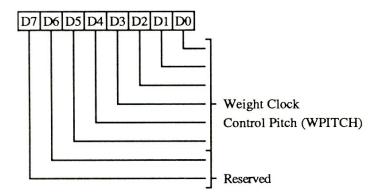

| 83                                           | WGTCLK                                 | (DE)  | Out                                     | High                                                 | WEIGHT CONTROL CLOCK or DISPLAY ENABLE. Grayscale reference clock for Panels with Pulse Width Modulation support. When clock masking is disabled (XR50D7=0), this pin is redefined as a Display Enable (DE) pin which qualifies the active display time.                                                     |

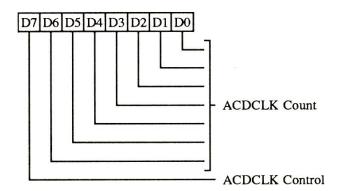

| 17                                           | ACDCLK                                 | (M)   | Out                                     | Both                                                 | LCD CLOCK. A 50% duty cycle square-wave with programmable period. Used to time the back bias switching in LCD panels.                                                                                                                                                                                        |

| Pin#                                                                    | Pin Name                                                 |           | Туре           | Active               | Description                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------------------------------------|----------------------------------------------------------|-----------|----------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 140                                                                     | ERMEN/                                                   | (GPOUT)   | Out            | Low                  | EARLY MEMORY INDICATOR. This output indicates whether display memory is being accessed by the CPU or by the 82C455 to refresh the display. High indicates display access and low indicates CPU access. This signal can be redefined as a general purpose output.                                                                                                                         |

| 112                                                                     | TRAP/                                                    | (CRT/LCD) | Out            | Low                  | TRAP. This active low output indicates a TRAP condition requiring special CPU assistance. This pin is open collector when used as a trap pin. It can be redefined as a general purpose output pin. The Chips BIOS redefines this as a CRT/LCD output. If this pin is high, the BIOS has programmed the part for CRT displays; if low, the BIOS has programmed the part for LCD displays. |

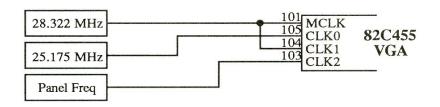

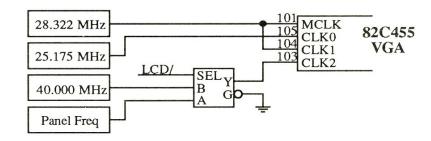

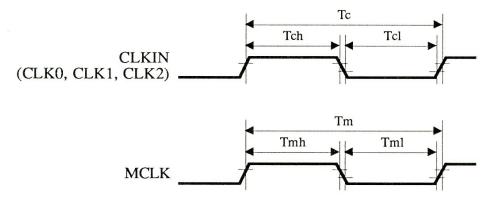

| 103<br>104<br>105                                                       | CLK2<br>CLK1<br>CLK0                                     |           | In<br>In<br>In | Both<br>Both<br>Both | CLOCK 2-0. Video Clock inputs. One of these dot clock inputs is selected by the Miscellaneous Output Register.                                                                                                                                                                                                                                                                           |

| 101                                                                     | MCLK                                                     |           | In             | Both                 | MASTER CLOCK. This clock input is used to sequence internal I/O cycles.                                                                                                                                                                                                                                                                                                                  |

| 1<br>18<br>54<br>73<br>90<br>126                                        | VCC<br>VCC<br>VCC<br>VCC<br>VCC                          |           | In             | n/a                  | POWER                                                                                                                                                                                                                                                                                                                                                                                    |

| 9<br>19<br>30<br>45<br>55<br>66<br>81<br>91<br>102<br>117<br>127<br>138 | GND                  |           | In             | n/a                  | GROUND                                                                                                                                                                                                                                                                                                                                                                                   |

| 36<br>37<br>106<br>107<br>109<br>110                                    | Reserved<br>Reserved<br>Reserved<br>Reserved<br>Reserved |           |                | je -                 | RESERVED. These pins are reserved and should be left unconnected.                                                                                                                                                                                                                                                                                                                        |

# 82C455 Registers

# GLOBAL CONTROL (SETUP) REGISTERS

The Setup Control Register is used to enable or disable the VGA. It is also used to place the VGA in normal or setup mode. This register is used only in the PC-bus interface. In the MCA Bus interface these functions are performed by the VGAENAB and SETUP/ pins respectively.

The Global and Extension Enable Registers are accessible <u>only during Setup mode</u>. The Global ID Register contains the ID number that identifies the 82C455 as a Chips & Technologies product.

Warning: In setup mode, the Global Setup Registers actually occupy the *entire I/O space*. Only the lower 3 bits are used to decode and select these registers. To avoid bus conflicts with other peripherals, reads should only be performed at the 10xh port addresses. This decode is compatible with the IBM VGA.

#### GENERAL CONTROL REGISTERS

Two Input Status Registers read the SENSE pin, pending CRT interrupt, display enable/HSYNC output, and vertical retrace/video output. The Feature Control Register selects the VSYNC function while the Miscellaneous Output Register controls I/O address select, clock selection, access to video RAM, memory page, and video SYNC polarity.

#### CGA / HERCULES REGISTERS

CGA Mode and Color Select registers are provided on-chip for emulation of CGA modes. Hercules Mode and Configuration registers are provided on-chip for emulation of Hercules mode.

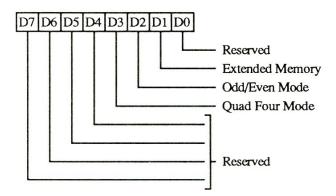

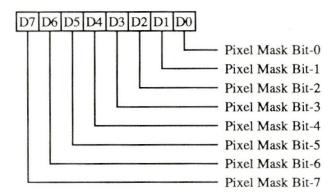

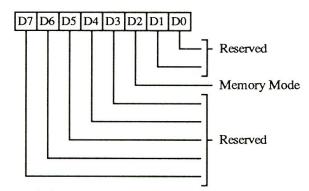

#### SEQUENCER REGISTERS

The Sequencer Index Register is a 3-bit index to the Sequencer Data Registers. The Reset Register forces an asynchronous or synchronous reset of the sequencer. The Sequencer Clocking Mode Register controls master clocking functions, video enable/disable and selects either an 8 or 9 dot character clock. A Plane/Map Mask Register enables the color plane and write protect. The Character Font Select Register handles video intensity and character generation and controls the display memory plane through the character generator select. The Sequencer Memory Mode Register handles all

memory, giving access by the CPU to 4/16/32KBytes, Odd/Even addresses (planes) and writing of data to display memory.

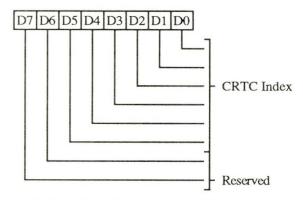

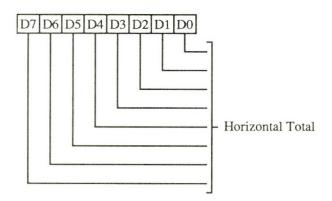

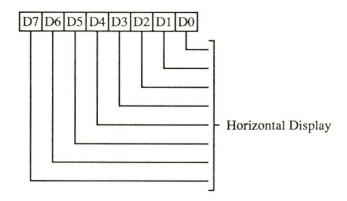

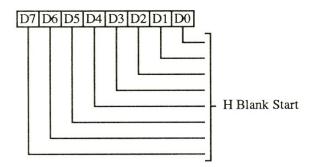

#### CRT CONTROLLER REGISTERS

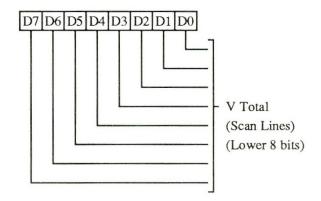

The CRT Controller Index Register is a 6-bit index to the CRT Controller Registers. Twenty eight registers perform all display functions for modes: horizontal and vertical blanking and sync, panning and scrolling, cursor size and location, light pen, and underline.

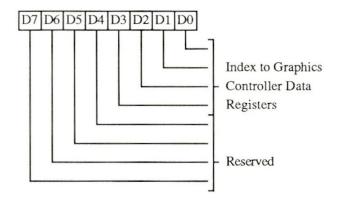

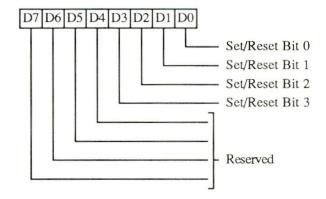

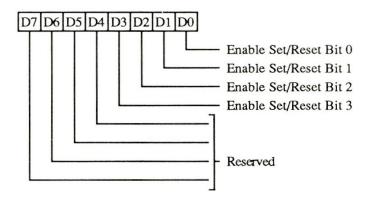

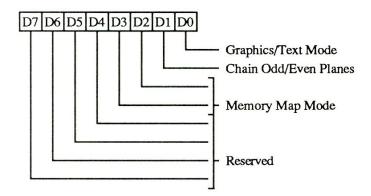

#### **GRAPHICS CONTROLLER REGISTERS**

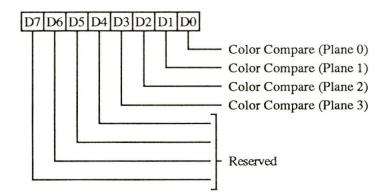

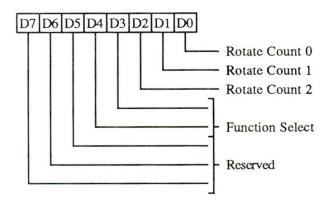

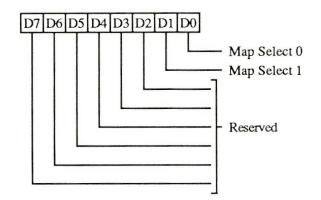

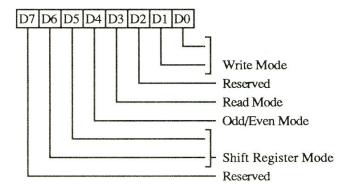

The Graphics Controller Index Register is a 4-bit index to the Graphics Controller Registers. The Set/Reset Register controls the format of the CPU data to display memory. It also works with the Enable Set/Reset Register. Reducing 32 bits of display data to 8 bits of CPU data is accomplished by the Color Compare Register. Data Rotate Registers specify the CPU data bits to be rotated and subjected to logical operations. The Read Map Select Register reduces memory data for the CPU in the four plane (16 color) graphics mode. The Graphics Mode Register controls the write, read, and shift register The Miscellaneous Register handles graphics/text, chaining of odd/even planes, and display memory mapping. Additional registers include Color Don't Care and Bit Mask.

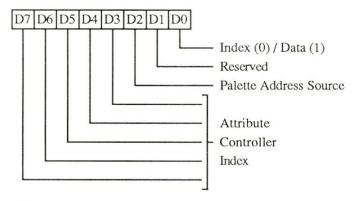

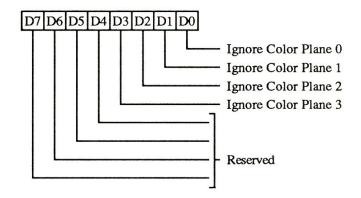

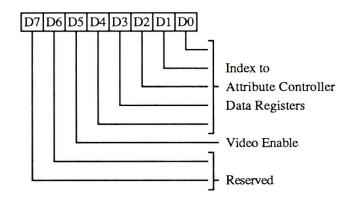

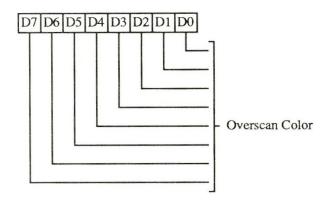

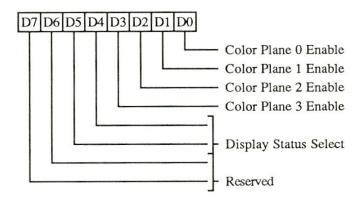

# ATTRIBUTE CONTROLLER AND EXTERNAL COLOR PALETTE REGISTERS

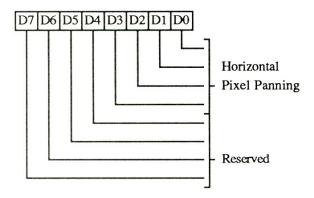

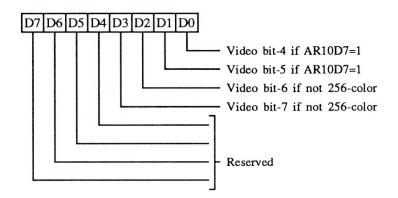

The Attribute Controller Index Register is a 5-bit index to the Attribute Controller Registers. A 6th bit is used to enable the video. The Attribute Controller Registers handle internal color lookup table mapping, text/graphics mode, overscan color, and color plane enable. The horizontal Pixel Panning and Pixel Padding Registers control pixel attributes on screen. External color palette registers handle CPU reads and writes to I/O address range 3C6h-3C9h. Some of the registers are located external to 82C455 in the external color palette. Inmos IMSG176 compatible registers are documented in this manual.

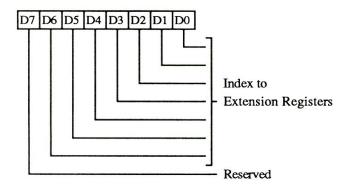

#### **EXTENSION REGISTERS**

The 82C455 defines a set of extension registers which are addressed with the 7-bit Extension Register Index. The I/O port address (3Bx/3Dxh)

and Read/Write access to the extension registers is controlled by the Extension Enable Register (103h). The extension registers handle a variety of interfacing, compatibility, and display functions as discussed below. They are grouped into the following logical groups for discussion purposes:

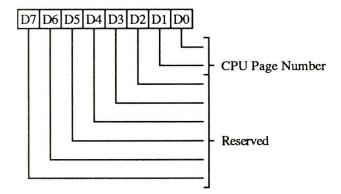

- 1. <u>Miscellaneous</u> Registers include the 82C455 Version number, Dip Switch CPU interface and paging control, memory mode control, power down/refresh control and diagnostic functions.

- 2. General Purpose Registers allow the CPU to individually switch two outputs (ERMEN/ and TRAP/). They also handle video blanking interface and the video default color.

- 3. <u>Backwards Compatibility</u> Registers control Hercules, MDA, and CGA emulation modes. Trap Enable and Trap Status as well as Write Protect functions are provided to increase flexibility in providing backwards compatibility.

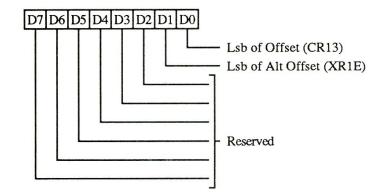

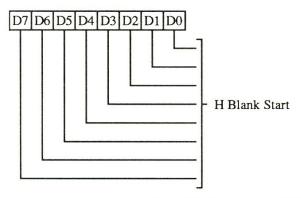

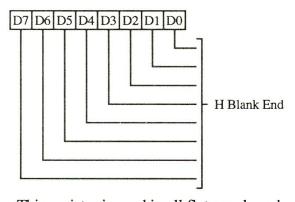

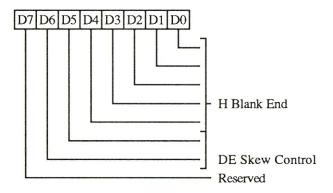

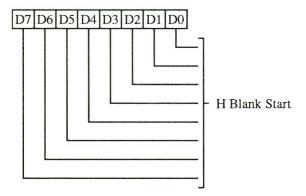

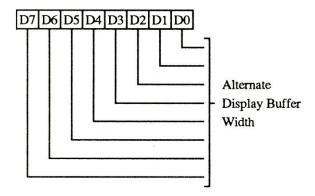

- 4. <u>Alternate Horizontal and Vertical</u> Registers handle all horizontal and vertical timing, including sync, blank and offset. These are used for both flat panels and backwards compatibility.

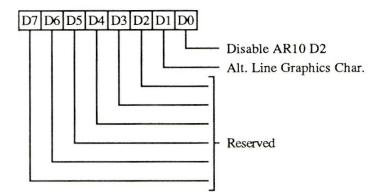

- 5. Panel Control Registers operate only in flat panel mode. The Panel Control Registers determine panel and video interface format display type and size, line drawing character function, and grayscale weighting and flat panel bias clocks.

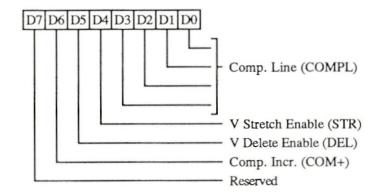

- 6. <u>Compensation</u> Registers provide vertical centering, blank line insertion, and graphics stretching features. For 350 and 400 line display modes, registers are provided to control display start and end locations, blank line insertion in text modes and stretching in both graphics and text modes.

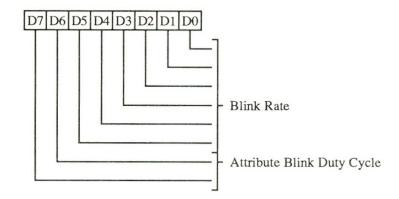

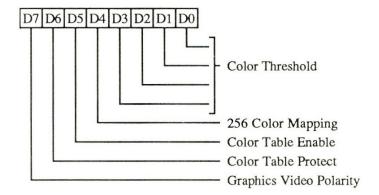

- 7. Color/Attributes Registers control Blink Rate, SmartMap<sup>™</sup> threshold, and shift parameters. A Graphics Color Mapping register controls color to monochrome threshold, VGA 256-color mapping, color lookup table protection, and graphics video polarity.

# 82C455 Global Control (Setup) Registers

| Register<br>Mnemonic | Register Name           | Index | Access | I/O<br>Address      | Protect<br>Group | Page |

|----------------------|-------------------------|-------|--------|---------------------|------------------|------|

| _                    | Setup Control           | _     | W      | 46E8h (PC-Bus only) | _                | 21   |

| _                    | Global Enable           | -     | RW     | 102h & Setup mode   | _                | 21   |

| _                    | <b>Extension Enable</b> | _     | RW     | 103h & Setup mode   | _                | 22   |

| _                    | Global ID               | _     | R      | 104h & Setup mode   | _                | 22   |

|                      |                         |       |        |                     |                  |      |

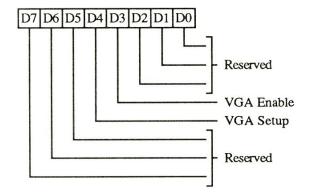

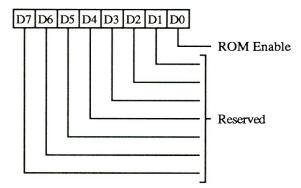

#### SETUP CONTROL REGISTER

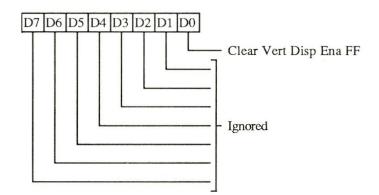

Write only at I/O Address 46E8h

This register is used with the PC-Bus Interface only. It is cleared by RESET. In the MCA interface, the Setup mode and VGA Disable are controlled through the SETUP/ and VGAENAB pins, respectively.

- **2-0** Reserved (0)

- 3 VGA Enable

- 0: VGA is disabled

- 1: VGA is enabled

- 4 Setup Mode

- 0: VGA is in Normal Mode

- 1: VGA is in Setup Mode

- 7-5 Reserved (0)

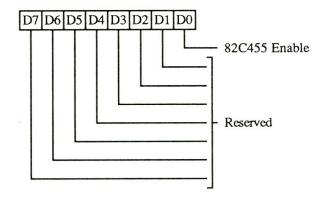

### **GLOBAL ENABLE REGISTER**

Read/Write at I/O Address 102h

This register is only accessible in Setup Mode. It is cleared by RESET.

- 0 VGA Enable

- 0: VGA is disabled

- 1: VGA is enabled

- **7-1** Reserved (0)

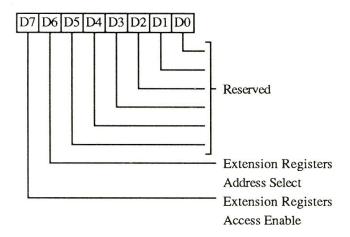

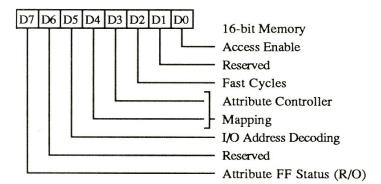

#### EXTENSION ENABLE REGISTER

Read/Write at I/O Address 103h

This register is only accessible in Setup Mode. It is cleared by RESET.

- **3-0** Reserved (0)

- 4 Reserved (0) This bit must be set to zero for proper operation of the 82C455.

- 5 Reserved (0)

- 6 Address for Extension Registers

- 0: Extension registers at I/O Address 3D6/3D7h

- 1: Extension registers at I/O Address 3B6/3B7h.

- 7 Extension Registers Access Enable

This bit controls access to the extension registers at 3D6/7 or 3B6/7. It also allows access to all CGA, MDA and Hercules registers in non-emulation mode.

0: Disable Access1: Enable Access

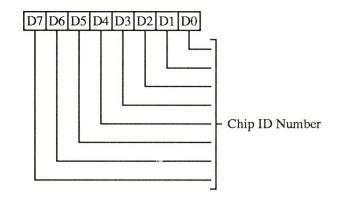

#### GLOBAL ID REGISTER

Read only at I/O Address 104h

This register is only accessible in Setup Mode.

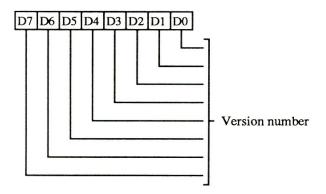

7-0 These bits contain the ID number (0A5h). This identifies the chip as a Chips and Technologies product.

# 82C455 General Control & Status Registers

| Register<br>Mnemonic | Register Name        | Index | Access | I/O<br>Address | Protect<br>Group | Page |

|----------------------|----------------------|-------|--------|----------------|------------------|------|

| ST00                 | Input Status 0       | -     | R      | 3C2h           | _                | 23   |

| ST01                 | Input Status 1       | _     | R      | 3BAh/3DAh      |                  | 23   |

| FCR                  | Feature Control      | _     | W      | 3BAh/3DAh      | 5                | 24   |

|                      |                      |       | R      | 3CAh           |                  |      |

| MSR                  | Miscellaneous Output | _     | W      | 3C2h           | 5                | 24   |

|                      |                      |       | R      | 3CCh           |                  |      |

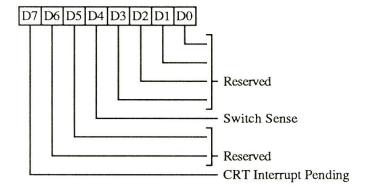

# **INPUT STATUS REGISTER 0 (ST00)**

Read only at I/O Address at 3C2h

- **3-0** Reserved (0)

- 4 Switch Sense. This bit returns the Status of the SENSE pin.

- 6-5 Reserved. These bits read back 00 in an AT bus implementation and 11 in MCA implementation.

- 7 CRT Interrupt Pending

- 0: Indicates no CRT interrupt is pending

- 1: Indicates a CRT interrupt is waiting to be serviced

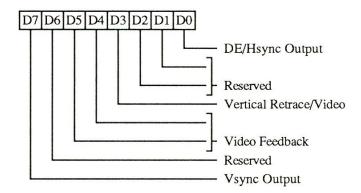

# **INPUT STATUS REGISTER 1 (ST01)**

Read only at I/O Address 3BAh/3DAh

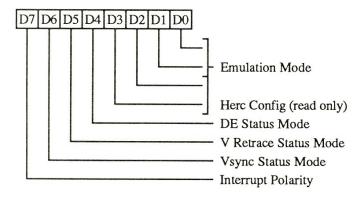

- O Display Enable/HSYNC Output. The functionality of this bit is controlled by the Emulation Mode register (XR14D4).

- 0: Indicates DE or HSYNC inactive

- 1: Indicates DE or HSYNC active

- **2-1** Reserved (0)

- Wertical Retrace/Video. The functionality of this bit is controlled by the Emulation Mode register (XR14D5).

- 0: Indicates VSYNC or video inactive

- 1: Indicates VSYNC or video active

- 5-4 Video Feedback 1, 0. These are diagnostic video bits which are selected via the Color Plane Enable Register.

- 6 Reserved (0)

- 7 Vsync Output. The functionality of this bit is controlled by the Emulation Mode register (XR14D6). It reflects the active status of the VSYNC output: 0=inactive, 1=active.

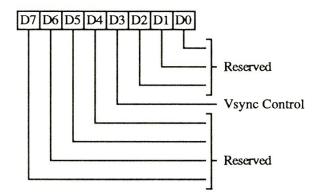

#### FEATURE CONTROL REGISTER (FCR)

Write at I/O Address 3BAh/3DAh Read at I/O Address 3CAh Group 5 Protection

- **2-0** Reserved (0)

- **3** Vsync Control This bit is cleared by RESET.

- 0: VSync output on the VSYNC pin

- 1: Logical 'OR' of VSync and Display Enable output on the VSYNC pin

- **7-4** Reserved (0)

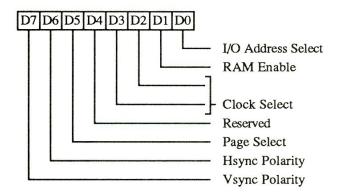

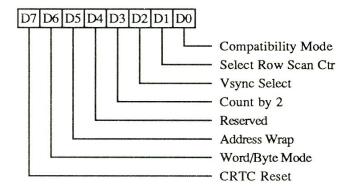

# MISCELLANEOUS OUTPUT REGISTER (MSR)

Write at I/O Address 3C2h Read at I/O Address 3CCh Group 5 Protection

This register is effective in CRT mode. The Alternate Miscellaneous Output register is used for bits 2,3,6 and 7 in flat panel mode. This register is cleared by RESET.

- 0 I/O Address Select. This bit selects 3Bxh or 3Dxh as the I/O address for the CRT Controller registers, the Feature Control Register (FCR), and Input Status Register 1 (ST01).

- 0: Select 3Bxh I/O address

- 1: Select 3Dxh I/O address

- 1 Enable RAM. 0: Prevent CPU access to display memory; 1: Allow CPU access to display memory.

- **3-2** Clock Select. These bits select the dot clock source for the CRT interface:

00 = Select CLK0

01 = Select CLK1

10 = Select CLK2

11 = Reserved

- 4 Reserved (0)

- Page Select. In Odd/Even Memory Map Mode 1 (GR06), this bit selects the upper or lower 64K byte page in display memory for CPU access: 1=select lower page; 0=select upper page.

- **6** CRT Hsync Polarity. 0=pos, 1=neg

- 7 CRT Vsync Polarity. 0=pos, 1=neg (Blank pin polarity can be controlled via the Video Interface Register)

# 82C455 CGA / Hercules Registers

| Register<br>Mnemonic | Register Name          | Index | Access | I/O<br>Address | Protect<br>Group | Page |

|----------------------|------------------------|-------|--------|----------------|------------------|------|

| MODE                 | CGA/Hercules Mode      | _     | RW     | 3D8h           | _                | 25   |

| COLOR                | CGA Color Select       | _     | RW     | 3D9h           | _                | 26   |

| HCFG                 | Hercules Configuration | _     | W      | 3BFh           | _                | 27   |

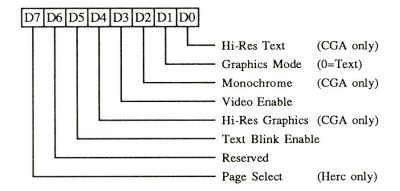

# CGA / HERCULES MODE CONTROL REGISTER (MODE)

Read/Write at I/O Address 3B8h/3D8h

This register is effective only in CGA and Hercules modes. It is accessible if CGA or Hercules emulation mode is selected or the extension registers are enabled. If the extension registers are enabled, the address is determined by the address select in the Miscellaneous Outputs register. Otherwise the address is determined by the emulation mode. It is cleared by RESET.

- 0 CGA 80/40 Column Text Mode

- 0: Select 40 column CGA text mode

- 1: Select 80 column CGA text mode

- 1 CGA/Hercules Graphics/Text Mode

- 0: Select text mode

- 1: Select graphics mode

- 2 CGA Mono/Color Mode

- 0: Select CGA color mode

- 1: Select CGA monochrome mode

- 3 CGA/Hercules Video Enable

- 0: Blank the screen

- 1: Enable video output

- 4 CGA High Resolution Mode

- 0: Select 320x200 graphics mode

- 1: Select 640x200 graphics mode

- 5 CGA/Hercules Text Blink Enable

- 0: Disable character blink attribute (blink attribute bit-7 used to control background intensity)

- 1: Enable character blink attribute

- **6** Reserved (0)

- 7 Hercules Page Select

- 0: Select the lower part of memory (starting address B0000h) in Hercules Graphics Mode

- 1: Select the upper part of the memory (starting address B8000h) in Hercules Graphics Mode

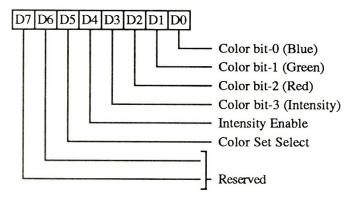

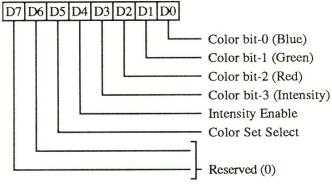

#### **CGA COLOR SELECT REGISTER**

Read/Write at I/O Address 3D9h

This register is effective only in CGA modes. It is accessible if CGA emulation mode is selected or the extension registers are enabled. This register may also be read or written as an Extension Register (XR7E). It is cleared by RESET.

### 3-0 Color

320x200 4-color:

Background Color (color when the pixel value is 0)

The foreground colors (colors when the pixel value is 1-3) are determined by bit-5 of this register.

640x200 2-color:

Foreground Color (color when the pixel

value is 1)

The background color (color when the pixel value is 0) is black.

4 Intensity Enable

Text Mode:

Enables intensified

background colors

320x200 4-color:

Enables intensified

colors 0-3

640x200 2-color:

Don't care

5 Color Set Select. This bit selects one of two available CGA color palettes to be used in 320x200 graphics mode (it is ignored in all other modes) according to the following table:

| Pixel<br>Value | Color Set<br>0     | Color Set<br>1     |  |  |

|----------------|--------------------|--------------------|--|--|

| 0 0            | Color per bits 0-3 | Color per bits 0-3 |  |  |

| 0 1            | Green              | Cyan               |  |  |

| 1 0            | Red                | Magenta            |  |  |

| 1 1            | Brown              | White              |  |  |

#### **7-6** Reserved (0)

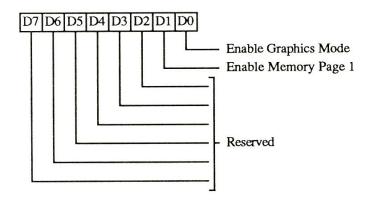

# HERCULES CONFIGURATION REGISTER (HCFG)

Write only at I/O Address 3BFh

This register is effective only in Hercules mode. It is accessible in Hercules emulation mode or if the extension registers are enabled. It may be read back through XR14D3&2. It is cleared by RESET.

# 0 Enable Graphics Mode

- 0: Lock the 82C455 in Hercules text mode. In this mode, the CPU has access only to memory address range B0000h-B7FFFh.

- 1: Permit entry to Hercules Graphics mode.

# 1 Enable Memory Page 1

- 0: Prevent setting of the Page Select bit (bit 7 of the Hercules Mode Control Register). This function also restricts memory usage to addresses B0000h-B7FFFh.

- 1: The Page Select bit can be set and the upper part of display memory (addresses B8000h BFFFFh) is available.

# **7-2** Reserved (0)

# 82C455 Sequencer Registers

| Register<br>Mnemonic | Register Name                      | Index | Access | I/O<br>Address | Protect<br>Group | Page |

|----------------------|------------------------------------|-------|--------|----------------|------------------|------|

| SRX                  | Sequencer Index                    | _     | RW     | 3C4h           | 1                | 29   |

| SR00                 | Reset                              | 00h   | RW     | 3C5h           | 1                | 29   |

| SR01                 | Clocking Mode                      | 01h   | RW     | 3C5h           | 1                | 30   |

| SR02                 | Plane/Map Mask                     | 02h   | RW     | 3C5h           | 1                | 30   |

| SR03                 | Character Font                     | 03h   | RW     | 3C5h           | 1                | 31   |

| SR04                 | Memory Mode                        | 04h   | RW     | 3C5h           | 1                | 32   |

| SR07                 | Horizontal Character Counter Reset | 07h   | W      | 3C5h           |                  | 32   |

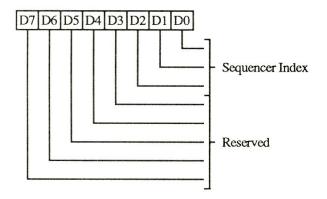

# SEQUENCER INDEX REGISTER (SRX)

Read/Write at I/O Address 3C4h

This register is cleared by RESET.

- 2-0 These bits contain a 3-bit Sequencer Index value used to access sequencer data registers at indices 0 through 7.

- 7-3 Reserved (0)

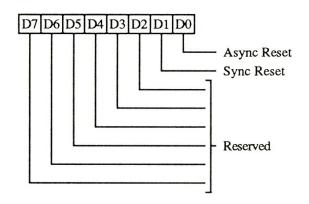

# **SEQUENCER RESET REGISTER (SR00)**

Read/Write at I/O Address 3C5h Index 00h Group 1 Protection

- 0 Asynchronous Reset

- 0: Force asynchronous reset

- 1: Normal operation

Display memory data will be corrupted if this bit is set to zero.

- 1 Synchronous Reset

- 0: Force synchronous reset

- 1: Normal operation

Display memory data is not corrupted if this bit is set to zero for a short period of time (a few tens of microseconds).

**7-2** Reserved (0)

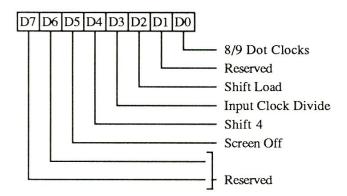

# SEQUENCER CLOCKING MODE REGISTER (SR01)

Read/Write at I/O Address 3C5h Index 01h Group 1 Protection

- 0 8/9 Dot Clocks. This bit determines whether a character clock is 8 or 9 dot clocks long.

- 0: Select 9 dots/character clock

- 1: Select 8 dots/character clock

- 1 Reserved (0)

- 2 Shift Load

- 0: Load video data shift registers <u>every</u> character clock

- 1: Load video data shift registers <u>every</u> <u>other</u> character clock

Bit-4 of this register must be 0 for this bit to be effective.

- 3 Input Clock Divide

- 0: Sequencer master clock output on the PCLK pin (used for 640 (720) pixel modes)

- 1: Master clock divided by 2 output on the PCLK pin (used for 320 (360) pixel modes)

- 4 Shift 4

- 0: Load video shift registers every 1 or 2 character clocks (depending on bit-2 of this register)

- 1: Load shift registers every 4th character clock.

- 5 Screen Off

- 0: Normal Operation

- 1: Disable video output and assign all display memory bandwidth for CPU accesses

- **7-6** Reserved (0)

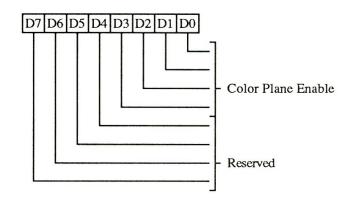

# SEQUENCER PLANE/MAP MASK REGISTER (SR02)

Read/Write at I/O Address 3C5h Index 02h Group 1 Protection

#### 3-0 Color Plane Enable

- 0: Write protect corresponding color plane

- 1: Allow write to corresponding color plane.

In Odd/Even and Quad modes, these bits still control access to the corresponding color plane.

# **7-4** Reserved (0)

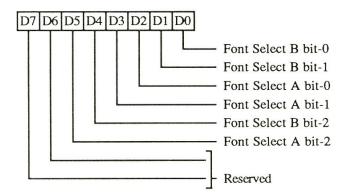

# CHARACTER FONT SELECT REGISTER (SR03)

Read/Write at I/O Address 3C5h Index 03h Group 1 Protection

In text modes, bit-3 of the video data's attribute byte normally controls the foreground intensity. This bit may be redefined to control switching between character sets. This latter function is enabled whenever there is a difference in the values of the Character Font Select A and the Character Font Select B bits. If the two values are the same, the character select function is disabled and attribute bit-3 controls the foreground intensity.

SR04D1 must be 1 for the character font select function to be active. Otherwise, only character fonts 0 and 4 are available.

- 1-0 Low order bits of Character Generator Select

- 3-2 Low order bits of Character Generator Select A

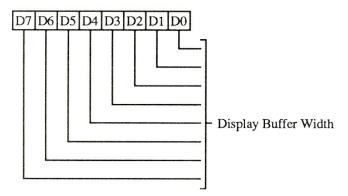

- 4 High order bit of Character Generator Select B